| Lugar ng pinagmulan: | Zhejiang |

| Pangalan ng Brand: | Inventchip Technology |

| Numero ng Modelo: | IVCR1402DPQR |

| Sertipikasyon: | AEC-Q100 kinikwalipika |

1. Mga Katangian

• Kapasidad ng driver current: 4A sink at source peak drive current

• Malawak na saklaw ng VCC hanggang 35V

• May integradong 3.5V negatibong bias

• Disenyado para sa low side at kaya para sa bootstrap high-side power

• UVLO para sa positibong at negatibong gate drive voltage

• Desaturation deteksyon para sa proteksyon sa short circuit may internong blanking time

• Fault output kapag nakita ang UVLO o DESAT

• 5V 10mA reference para sa panlabas na circuit, halimbawa digital isolator

• Mga input na maaaring magtrabaho sa TTL at CMOS

• SOIC-8 may pinakamahusay na pad para sa mataas na frekwentse at kapangyarihan na aplikasyon

• Mababang pagpapalit ng delai 45ns tipikal mayroong ipinangakong de-glitch filter

• AEC-Q100 na pinagana

2. Mga Gamit

• EV On Board Chargers

• EV/HEV inwerter at estasyon ng pagcharge

• AC/DC at DC/DC converter

• Motor Drive

3. Pagsipi

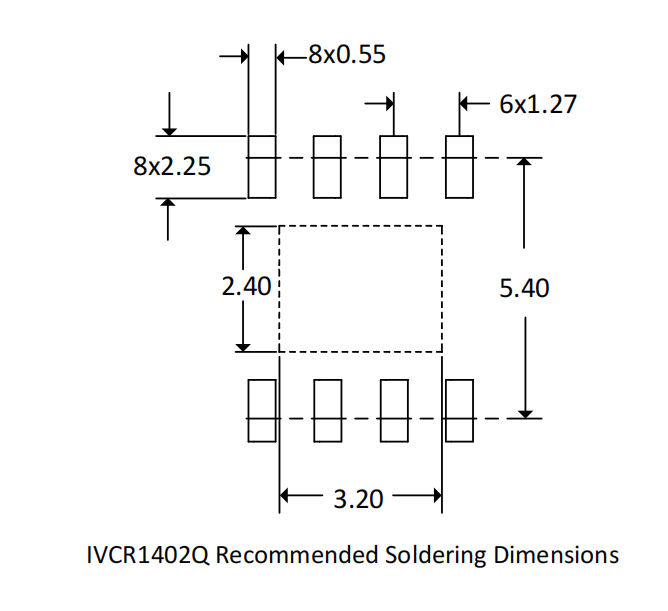

Ang IVCR1402Q ay isang AEC-Q100 na pinagkuhanan, 4A single-channel, mabilis na smart driver, kaya ng maikli at ligtas na magtrabaho sa SiC MOSFETs at IGBTs. Matibay ang pag-drive kasama ang negatibong bias na nagpapabuti sa resistensya sa ruido laban sa epekto ng Miller sa mataas na dv/dt operasyon. Ang deteksyon ng desaturation ay nagbibigay ng matibay na proteksyon sa maikling circuit at nakakabawas sa panganib ng pinsala sa power device at mga komponente ng sistema. Isina-insert ang itinakdang 200ns blanking time upang maiwasan ang pag-trigger nang maaga ng proteksyon sa sobrang current dahil sa spike at ruido ng switching edge current. Itinatakda na positibong gate drive voltage UVLO at itinakdang negatibong bias UVLO proteksyon upang siguraduhin ang malusog na gate operation voltages. Ang aktibong low fault signal ay nagbabahaging balita sa sistema kapag may UVLO o sobrang current. Mababang pag-propagate ng pagka-delay at mismatch kasama ang inilalabas na thermal pad ay nagpapahintulot sa SiC MOSFETs na mag-switch sa daanan ng kHz. Nakakabilang ang integradong negatibong pag-generate ng voltage at 5V reference output na minuminsan ang bilang ng mga eksternal na komponente. Ito ang unang industriyal na SiC MOSFET at IGBT driver na kasama ang negatibong pag-generate ng voltage, desaturation at UVLO sa isang 8-pin package. Ito ang ideal na driver para sa kompaktng disenyo.

Impormasyon ng Dispositibo

| PARTNUMBER | PACKAGE | Pagbabalot | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP) | Tape at Reel | ||||||||||||||||||

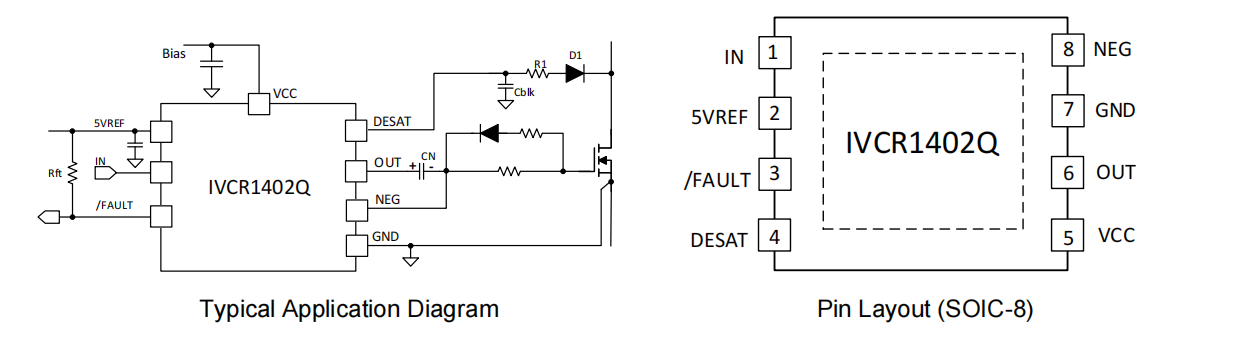

4. Paggamit at Mga Kabisa ng mga Pin

| pin | Pangalan | I/O | Paglalarawan | |||||||||||||||||||||||||||||||||||||||||

| 1 | sa | Ako | Input ng Looban | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | O | 5V/10mA output para sa panlabas na circuit | |||||||||||||||||||||||||||||||||||||||||

| 3 | /FAULT | O | Open collector fault output, inilalagay sa mababa kapag may over current o UVLO ay nakikita. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | Ako | Input ng deteksyon ng desaturation | |||||||||||||||||||||||||||||||||||||||||

| 5 | VCC | P | Positibong supply ng bias | |||||||||||||||||||||||||||||||||||||||||

| 6 | Labas | O | Output ng gate driver | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | g | Driver ground | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | O | Negatibong output ng voltas | |||||||||||||||||||||||||||||||||||||||||

| Inilalagay na pad | Madalas ay kinakabit ang ibabang inilalagay na pad sa GND sa layout. | |||||||||||||||||||||||||||||||||||||||||||

5. Mga Espekisipikasyon

5.1 Mga Pinakamataas na Rating

Sa temperatura ng libreng hangin (maliban kung iba ay tinukoy) (1)

| min max | yunit | ||||||||||||||||||||||||||||||||||||||||||

| Kabuuang supply voltage ng VCC (pamudmod sa GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| VOUT Voltage ng output ng gate driver | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH Dugong source current ng gate driver output (sa pinakamalaking pulse width na 10us at 0.2% duty cycle) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| IOUTL Dugong sink current ng gate driver output (sa pinakamalaking pulse width na 10us at 0.2% duty cycle) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| VIN IN signal voltage | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF Dugo sa output ng 5VREF | 25 | ina | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Voltage sa DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| VNEG Ulat sa NEG pin | OUT-5.0 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| TJ Junction temperatura | -40 150 | °C | |||||||||||||||||||||||||||||||||||||||||

| TSTG Pagmamahalang temperatura | -65 150 | °C | |||||||||||||||||||||||||||||||||||||||||

(1) Ang pag-operate sa labas ng mga itinakda sa Absolute Maximum Ratings ay maaaring magdulot ng pribimitibong pinsala sa kagamitan.

Ang pagpapaloob sa absolute maximum rated conditions sa isang mahabang panahon ay maaaring maiham ang relihiyon ng kagamitan.

5.2 ESD Rating

| halaga | yunit | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Elektrostatikong diskarga | Modelo ng katawan ng tao (HBM), ayon sa AEC Q100-002 | +/-2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Charged-device model (CDM), ayon sa AEC Q100-011 | +/-500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 Inirerekomenda na Mga Kondisyon sa Operasyon

| Min | Max | yunit | ||||||||||||||||||||||||||||||||||||||||||

| Kabuuang supply voltage ng VCC (pamudmod sa GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| Voltage ng input sa pultahan ng VIN | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Voltage sa DESAT | 0 | VCC | V | |||||||||||||||||||||||||||||||||||||||||

| Temperatura ng paligid ng TAMB | -40 | 125 | °C | |||||||||||||||||||||||||||||||||||||||||

5.4 Impormasyong Termodiniko

| IVCR1402DPQR | yunit | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Junction-to-Ambient | 39 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Mgaugangay-sa-PCB | 11 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJP Mgaugangay-sa-pad na pinalalagay | 5.1 | °C/W | |||||||||||||||||||||||||||||||||||||||||

5.5 Elektrikal na Espekipikasyon

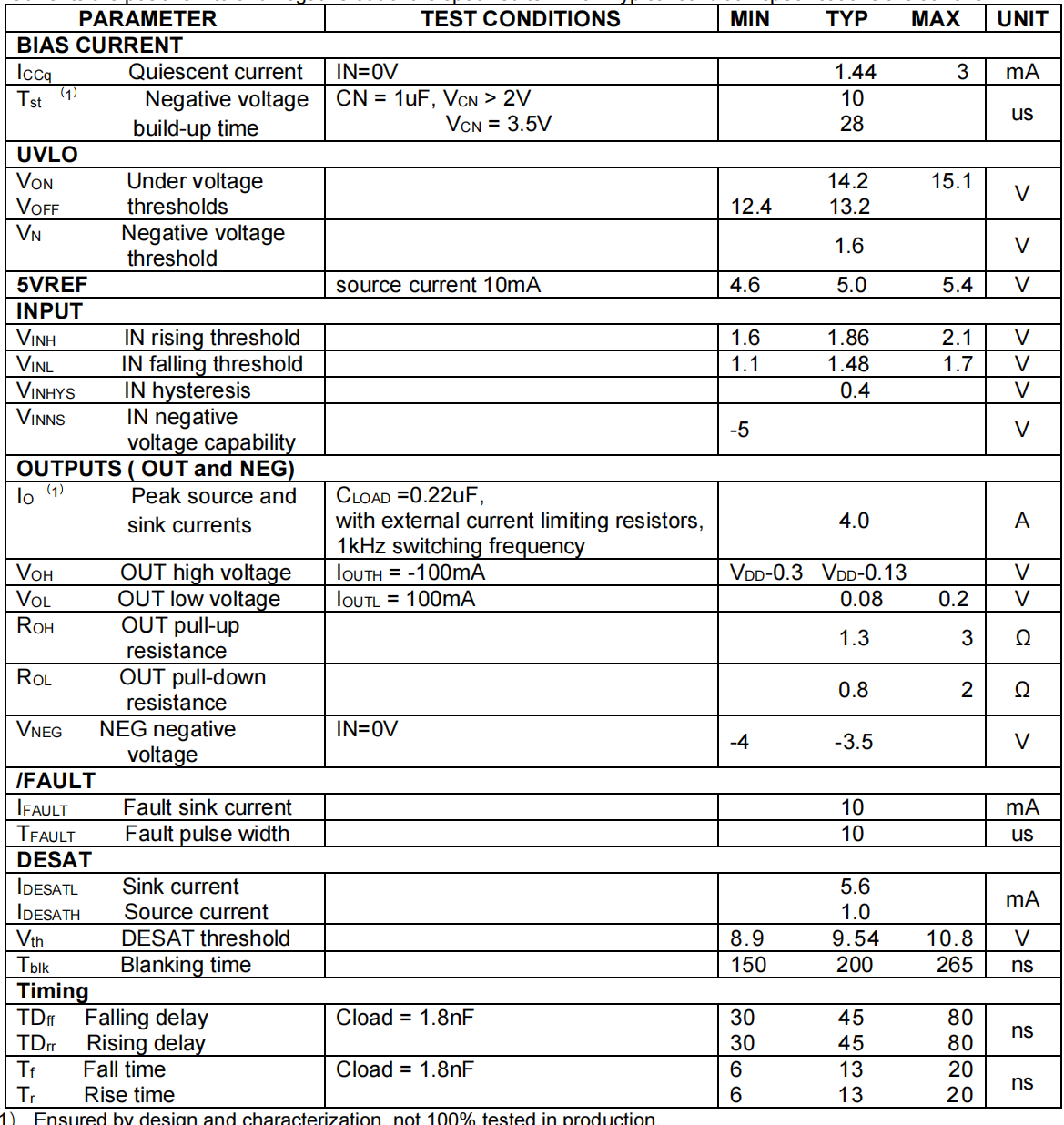

Maliban kung iba ang tinukoy, VCC = 25 V, TA = –40°C hanggang 125°C, 1-μF bypass capacitance mula sa VCC patungong GND, f = 100 kHz.

Ang mga corrent ay positibo pumasok at negatibo lumalabas sa tinutukoy na terminal. Ang mga tipikal na kondisyon ng espekipikasyon ay nasa 25°C.

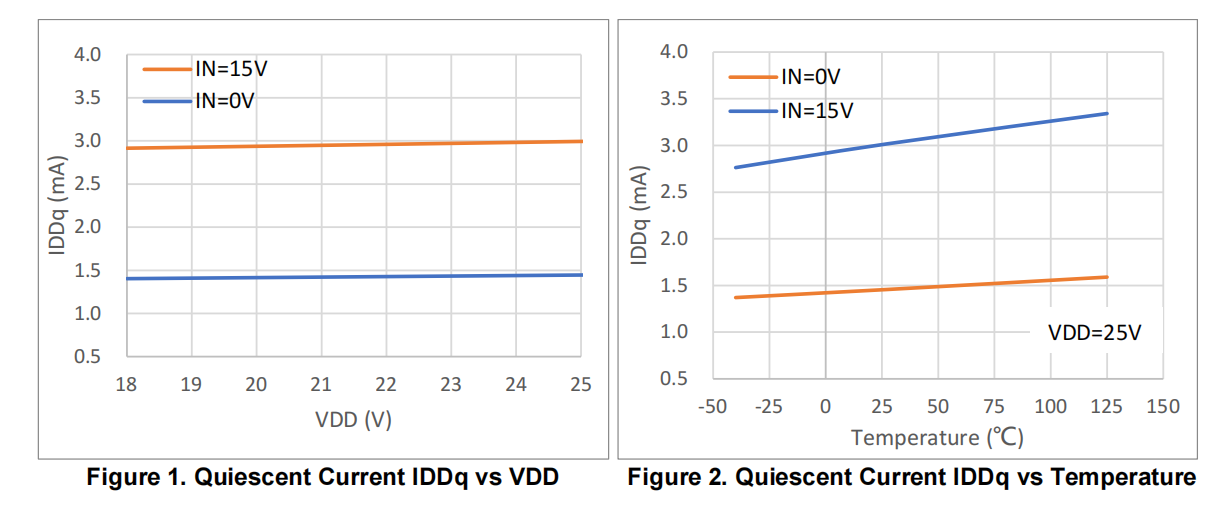

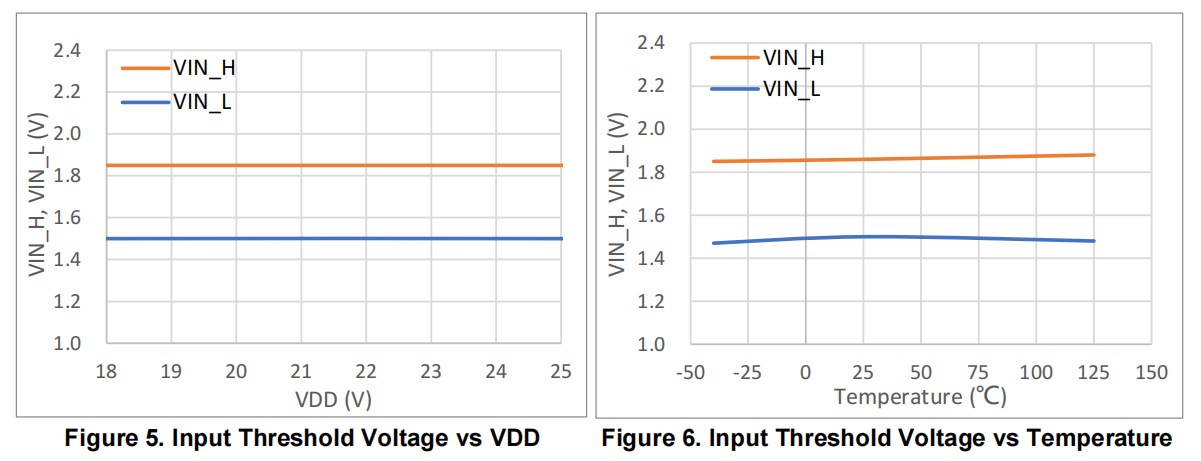

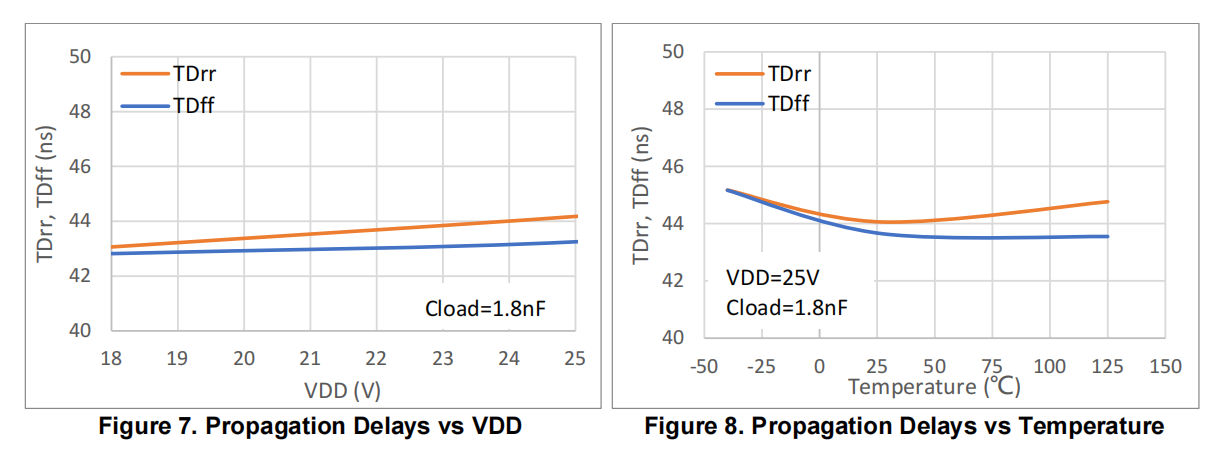

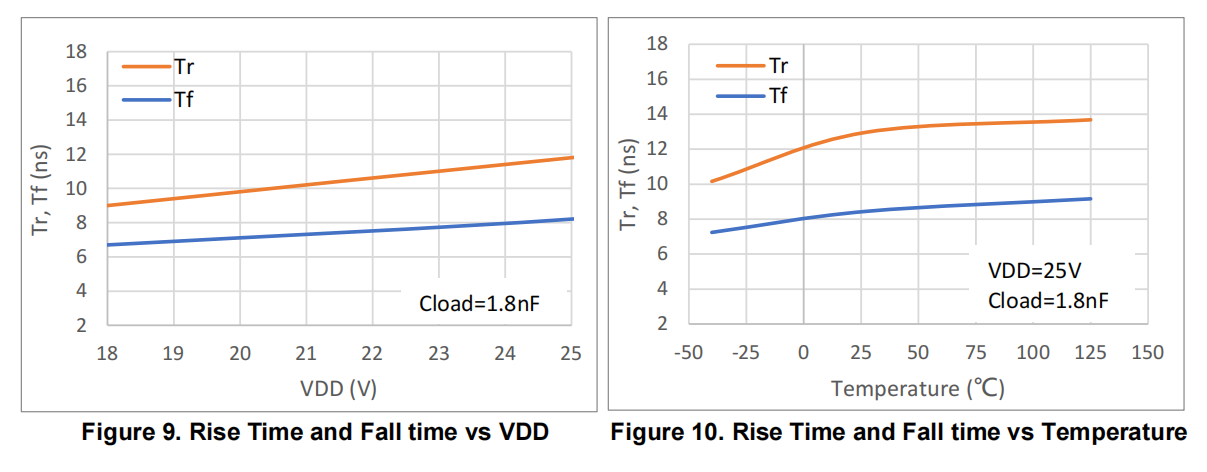

6 Tipikal na Karakteristik

7 Detalyadong Pagsipi

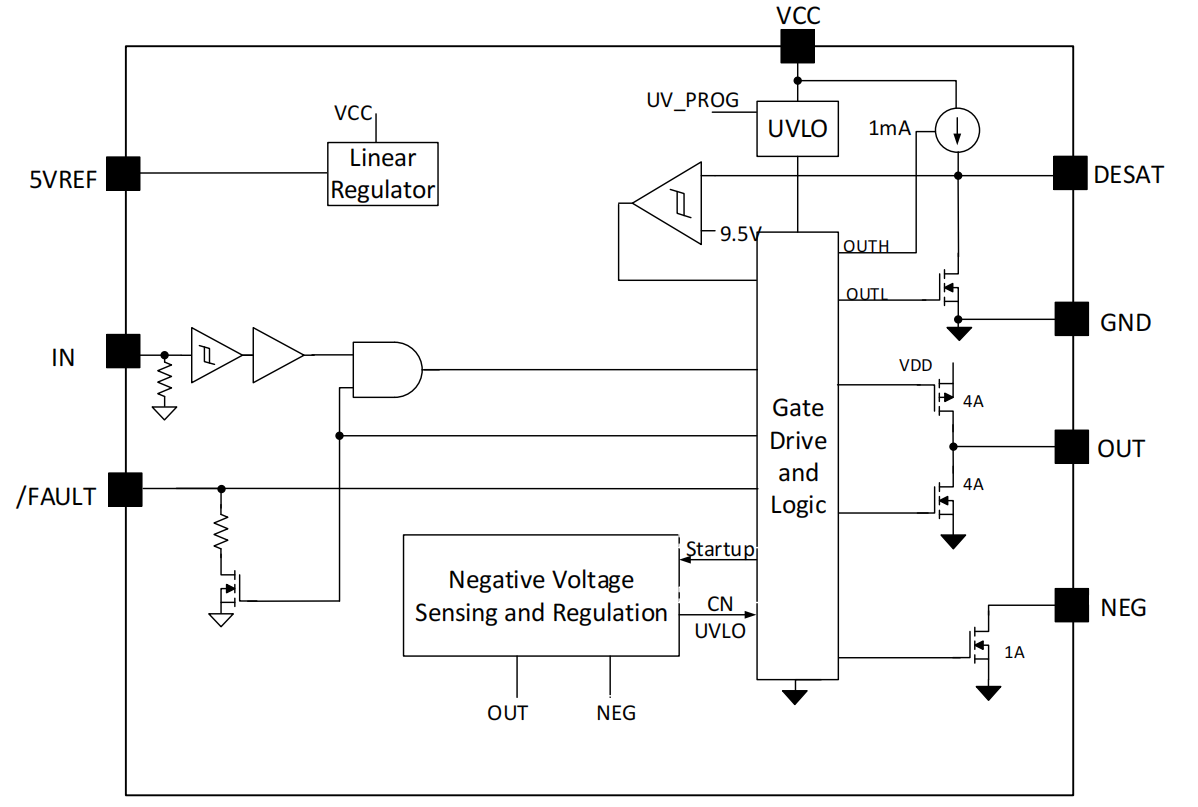

IVCR1402Q driver ay kinakatawan ng pinakabagong teknolohiya ng single channel low-side high-speed gate driver ng InventChip

may built-in negative voltage generation, desaturation/short-circuit protection,

programmable UVLO. Nag-aalok ang driver na ito ng pinakamahusay sa klase na katangian at ang pinakakompaktong at pinakatitiyak

SiC MOSFET gate driving control. Ito ang unang driver sa industriya na may lahat ng kinakailangang mga tampok ng SiC MOSFET gate sa isang SOIC-8 package.

driving tampok sa isang SOIC-8 package.

Function Block Diagram

7.1 Input

IN ay isang non-inverting logic gate driver input. Mayroong mahina pulldown sa pin. Ang input ay kompyable sa TTL at CMOS logic level na may maximum 20V input tolerance.

compatible logic level na may maximum 20V input tolerance.

7.2 Output

IVCR1402Q ay may 4A totem-pole output stage. Ito ay nagdadala ng mataas na source current kapag kailangan ito nang higit sa lahat sa rehiyon ng Miller plateau ng paglipat ng power switch turn-on transition. Ang malalakas na sink capability ay humihikayat sa mababang pull-down impedance sa output stage ng driver na nagpapabuti sa resistance laban sa parasitic Miller.

kinakailangan ito nang higit sa lahat sa rehiyon ng Miller plateau ng paglipat ng power switch turn-on transition. Malalakas na sink capability ay humihikayat sa mababang pull-down impedance sa driver output stage na nagpapabuti sa resistance laban sa parasitic Miller.

isang mababang pull-down impedance sa driver output stage na nagpapabuti sa resistance laban sa parasitic Miller

pag-on epekto, lalo na kung ang mababang gate-charge Si MOSFETs o umuusbong malawak na bandgap SiC MOSFETs ay

ginamit.

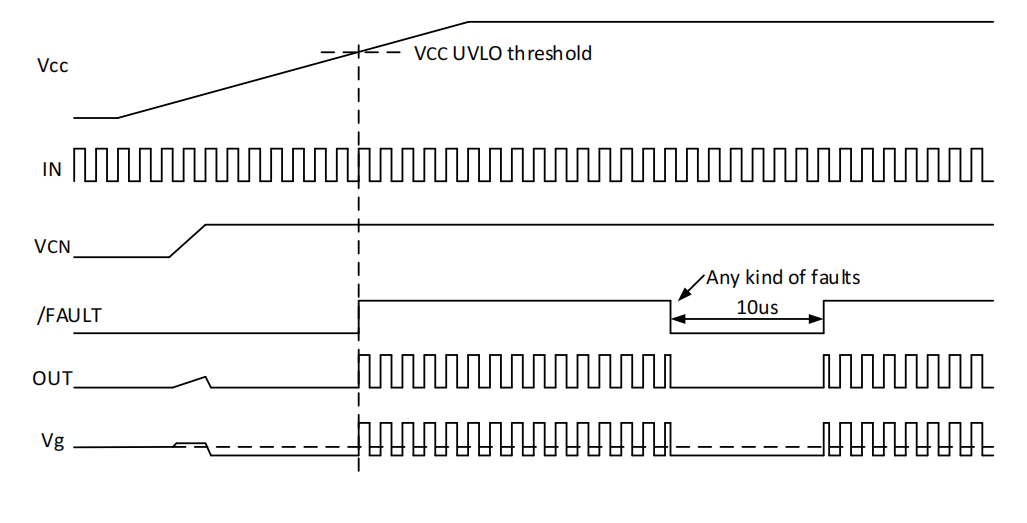

7.3 Paglikha ng Negatibong Voltage

Sa startup, NEG output ay pulls sa GND at nagbibigay ng isang mataas na kasalukuyang landas para sa isang kasalukuyang mapagkukunan upang singilin ang

ang panlabas na negatibong voltay capacitor CN (1uF na karaniwan) sa pamamagitan ng OUT pin. Ang capacitor ay maaaring ma-charge sa itaas

2.0V sa mas mababa sa 10us. Bago ang capacitor boltahe, VCN, singilin up, / fault mananatili mababang / aktibong, hindi isinasaalang-alang

Ang antas ng lohika ng IN. Pagkatapos ng negatibong bias ay handa, parehong NEG pin at / FAULT pin ay inilabas at OUT nagsisimula upang

Sundin ang input signal na IN. Ang isang built-in na negatibong boltahe regulator ay nagregular sa negatibong boltahe sa -3.5V para sa normal

operasyon, anuman ang PWM frequency at duty cycle. Ang signal ng gate drive, NEG, pagkatapos ay lumipat sa pagitan ng

VCC-3.5V at -3.5V.

7.4 Sa ilalim ng Proteksyon ng Voltage

Ang lahat ng panloob at panlabas na biases ng driver ay sinusubaybayan upang matiyak ang isang malusog na kondisyon ng operasyon. Ang VCC ay

sinusubaybayan ng isang under voltage detection circuit. Ang driver output ay pinutol (pinutol sa mababang) o mananatili mababang kung ang

ang boltahe ay nasa ibaba ng itinakdang limitasyon. Tandaan na ang VCC UVLO threshold ay 3.5V na mas mataas kaysa sa mga boltahe ng gate.

Sinusubaybayan din ang negatibong boltahe. Ang UVLO nito ay may isang nakapirming 1.6V na negatibong-pagpunta ng threshold. Negatibong boltahe

Ang depekto ng capacitor ay maaaring magresulta sa voltage ng capacitor sa ibaba ng threshold. Ang UVLO proteksyon ay pagkatapos ay pull

Ang gate ng MOSFET ay nasa lupa. Ang / FAULT ay pinapababa kapag nakita ang UVLO.

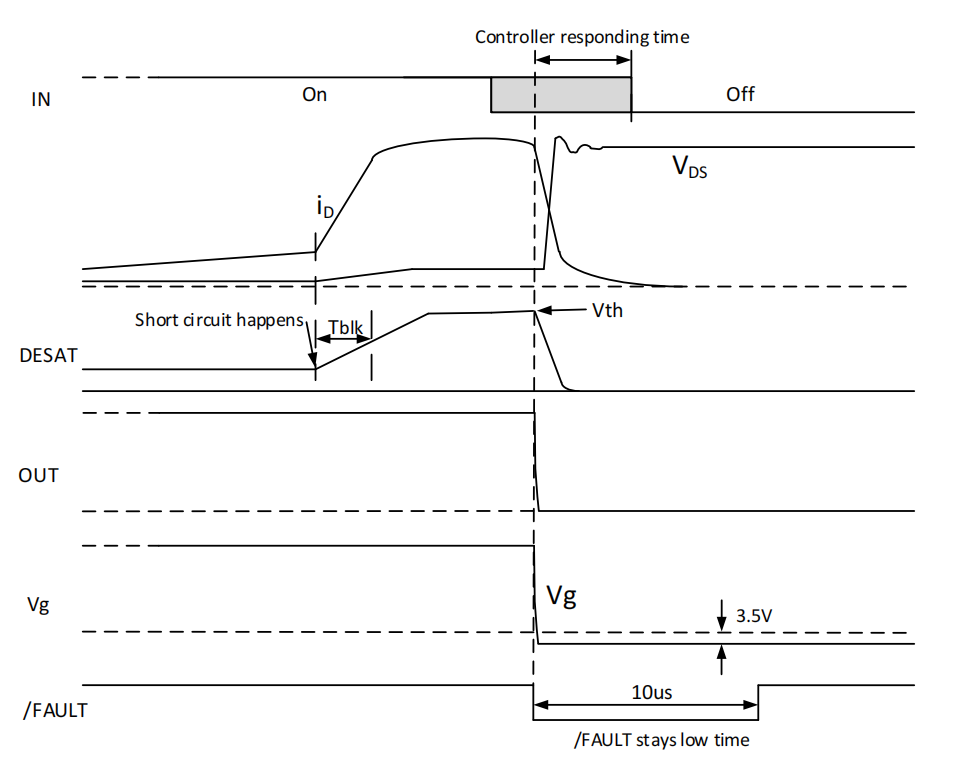

7.5 Pagtuklas ng Desaturation

Kapag short circuit o higit sa kasalukuyang nangyayari, ang kapangyarihan aparatos (SiC MOSFET o IGBT) drain o kolektor

kasalukuyang maaaring tumaas sa isang mataas na halaga na ang mga aparato makakuha ng out ng saturation estado, at Vds/Vce ng

ang mga device ay tataas sa isang malaking halaga. Ang DESAT pin na may blanking capacitor Cblk, karaniwang tinatambak sa

Id x Rds_on, ngayon ay maaaring magcharge nang mas mataas sa pamamagitan ng isang 1mA constant current source sa loob. Kapag umabot ang

voltage sa tipikal na 9.5V threshold, sinusunod ang OUT at /FAULT sa low. Isinasama ang isang 200ns blank time

sa pagtaas ng edge ng OUT upang maiwasan ang ma-trigger ng DESAT protect circuit dahil sa pagsisisi ng Coss.

Upang minimizahin ang pagkawala ng panloob na constant current source, natatapos ang current source kapag nasa off state ang pangunahing switch

maaari mong iprogram ang turn-off delay time (external blanking time) sa pamamagitan ng pagpili ng iba't ibang capacitance.

maaaring ikalkula ang blanking time gamit ang

Teblk = Cblk ∙Vth ∕ IDESAT

Halimbawa, kung ang Cblk ay 47pF, Teblk = 47pF ∙9.5V ∕ 1mA = 446ns.

Tandaan na kasama na ang internal Tblk 200ns blanking time sa Teblk.

Para sa pagtatakda ng kasalukuyang limitasyon, maaaring gamitin ang sumusunod na ekwasyon,

Ilimit = (Vth – R1* IDESAT – VF_D1)\/ Rds_on

kung saan ang R1 ay isang programming resistor, VF_D1 ay forward voltage ng high voltage diode, Rds_on ay SiC MOSFET turn

on resistance sa tinatayang temperatura ng junction, tulad ng 175C.

Ang iba't ibang power system ay karaniwang kailangan ng iba't ibang turn-off time. Ang pinag-optimang turn-off time ay maaaring makamit ang pinakamalaking kapansin-pansin ng sistema sa mga sitwasyong short circuit habang sinusuri ang Vds at bus voltage ringing.

ang sistema short circuit capability habang sinusuri ang Vds at bus voltage ringing.

7.6 Fault

\/FAULT ay isang open collector output na walang panloob na pull-up resistance. Kapag nakikita ang desaturation at under voltages, ang \/FAULT pin at OUT ay parehong binababa. Ang \/FAULT signal ay mananatiling mababa sa loob ng 10us matapos ang fault condition ay inalis.

\/FAULT ay isang auto recovery signal. Kailangan ng system controller na pumasya kung paano

gawin ito.

upang makasagot sa \FAULT signal. Ang sumusunod na diagram ay nagpapakita ng sequence ng signal.

7.7 NEG

Ang panlabas na kapasitor ng negative bias ay mabilis na nasisira kapag ang NEG ay umabot sa low. Nagaganap ito habang nagigising ang powers up

at ang taon ng pagbabalik-buhay bago matapos ang 10us \FAULT low period matapos anumang sugat ay tinukoy. Habang nagigising ang powers up

at sa panahon ng pagbabalik-buhay, masusukat ang voltasyon ng kapasitor ng negative bias VCN. Pagkatapos na ang voltasyon ay lumampas sa VN

UVLO threshold, ang NEG ay magiging high-impedance at ang OUT ang kumukuha ng kontrol sa gate drive.

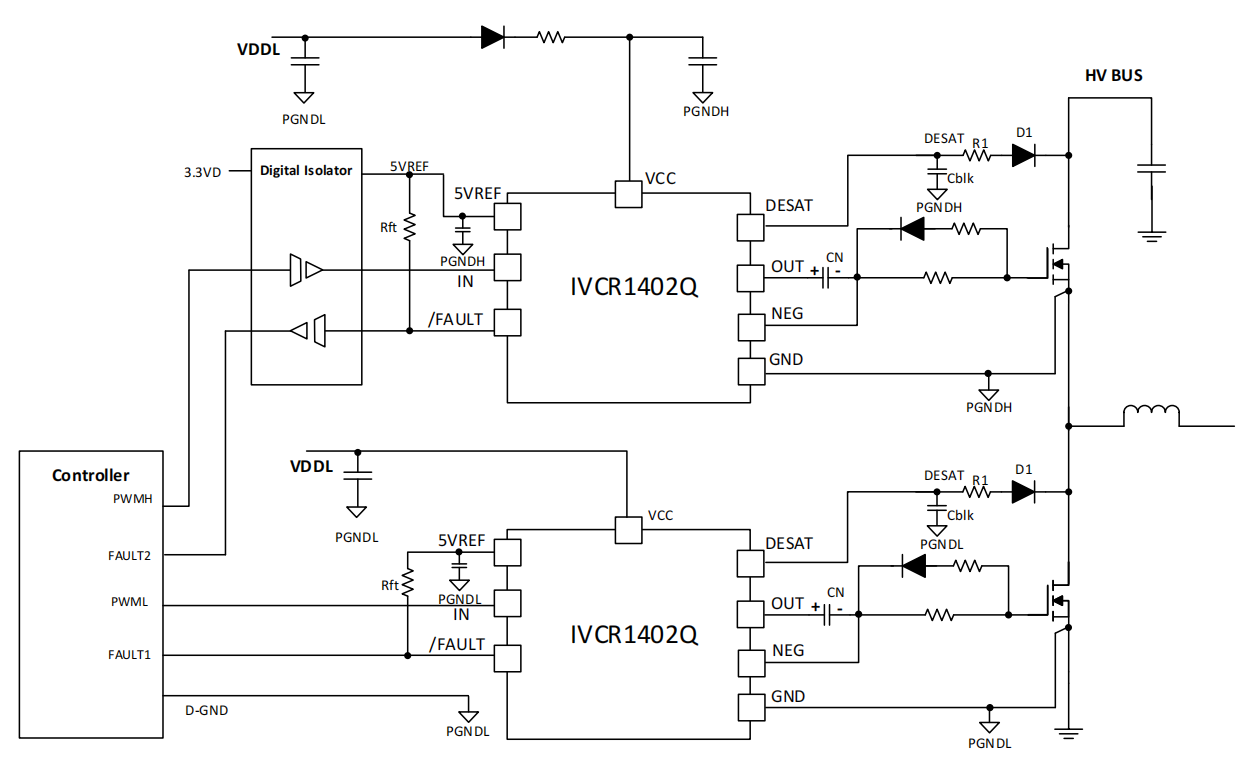

8 Mga Aplikasyon at Implementasyon

IVCR1402Q ay isang ideal na driver para sa kompakto na disenyo. Ito ay isang low-side driver. Gayunpaman, mayroong built-in

negative voltage generator, maaaring gamitin ang driver bilang high-side driver nang hindi gumagamit ng isolated bias.

Maaaring gamitin ang isang mura na bootstrap sa halip. Ang sumusunod na circuit diagram ay nagpapakita ng tipikal na half bridge

aplikasyon ng driver.

9 Layout

Ang mabuting layout ay isang mahalagang hakbang upang makamit ang nais na pagganap ng circuit. Ang matibay na lupa ang unang dapat simulan.

Inirerekomenda na i-bind ang nakikitang pad sa lupa ng driver. Ito ay isang pangkalahatang panuntunan na ang mga capacitor ay may

isang mas mataas na priyoridad kaysa sa mga resistors para sa lokasyon arrangement. Ang isang 1uF at isang 0.1uF decoupling capacitors

dapat na malapit sa VCC pin at grounded sa ground plane ng driver. Negative boltahe capacitor ay dapat

ilagay malapit sa OUT at NEG pin. Ang blanking capacitor ay dapat na malapit sa driver din. Isang maliit na filter

(with10ns time constant) ay maaaring kinakailangan sa input ng IN kung ang mga input signal traces ay upang lumipas

sa pamamagitan ng isang maingay na lugar. Ang sumusunod ay isang inirerekomendang layout.

10 Impormasyon sa Packaging

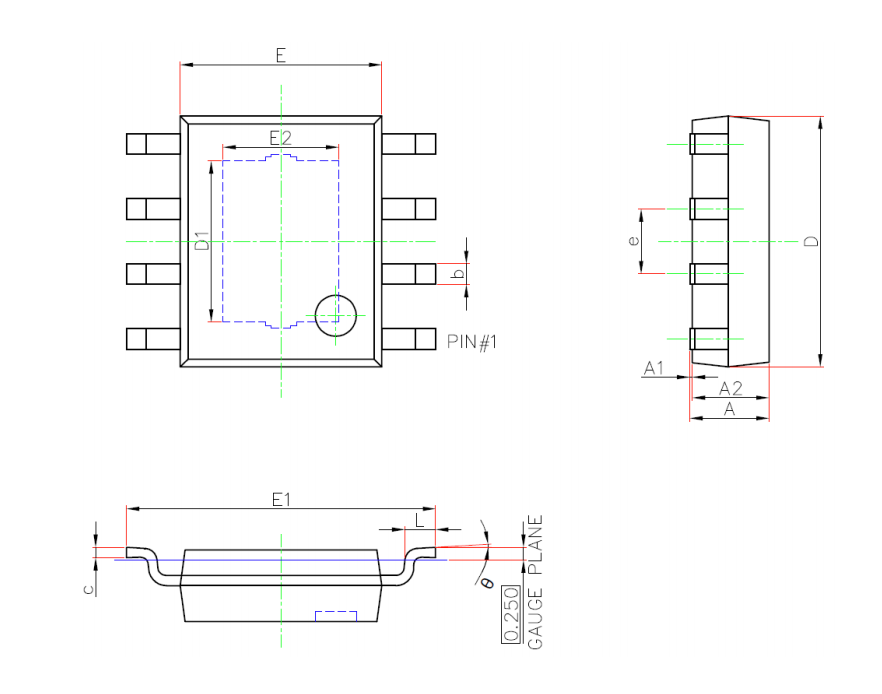

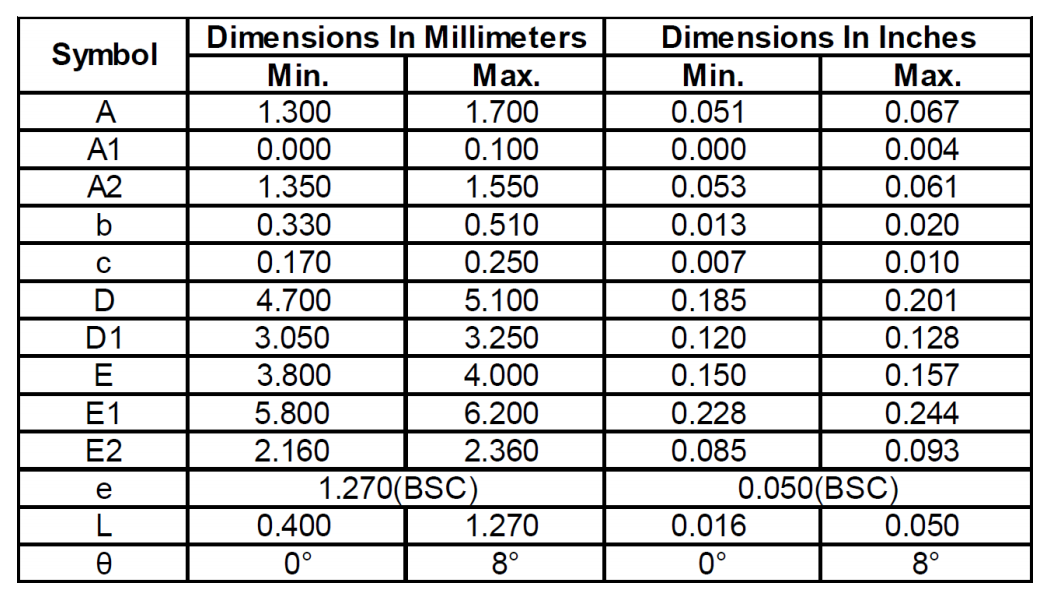

Mga Sukat ng Pakete ng SOIC-8 (EP)