| Local de Origem: | Zhejiang |

| Nome da Marca: | Inventchip Technology |

| Número do Modelo: | IVCR1402DPQR |

| Certificação: | AEC-Q100 qualificado |

1. Recursos

• Capacidade de corrente do driver: 4A pico de corrente de saída e entrada

• Faixa ampla de VCC até 35V

• Polarização negativa integrada de 3,5V

• Projetado para o lado baixo e adequado para alimentação do lado alto por bootstrap

• UVLO para tensão de condução positiva e negativa

• Detecção de desatuação para proteção contra curto-circuito com tempo de ocultação interno

• Saída de falha quando UVLO ou DESAT for detectado

• Referência de 5V 10mA para circuito externo, ex. isolador digital

• Entrada compatível com TTL e CMOS

• SOIC-8 com pino exposto para aplicações de alta frequência e potência

• Baixo atraso de propagação, típico de 45ns, com filtro de eliminação de glitches integrado

• Qualificado AEC-Q100

2. Aplicações

• Carregadores a Bordo para VE

• Inversores e estações de carregamento para VE/HEV

• Conversores AC/DC e DC/DC

• Acionamento de Motores

3. Descrição

O IVCR1402Q é um driver inteligente de alta velocidade, qualificado AEC-Q100, com 4A em um único canal, capaz de conduzir eficientemente e de forma segura MOSFETs de SiC e IGBTs. Uma condução forte com viés negativo melhora a imunidade ao ruído contra o efeito Miller em operações de alta dv/dt. A detecção de desativação fornece uma robusta proteção contra curto-circuito e reduz o risco de danos aos dispositivos de potência e componentes do sistema. Um tempo de bloqueio fixo de 200ns é inserido para evitar que a proteção contra corrente excessiva seja acionada prematuramente por picos de corrente e ruído na borda de comutação. Proteção UVLO de tensão positiva de condução fixa e viés negativo fixo garantem tensões de condução saudáveis nos terminais. Um sinal de falha ativo em nível baixo alerta o sistema quando ocorre UVLO ou corrente excessiva. Baixa propagação de atraso e desajuste, com um pad térmico exposto, permite que os MOSFETs de SiC comutem em centenas de kHz. A geração integrada de tensão negativa e saída de referência de 5V minimiza o número de componentes externos. É o primeiro driver industrial de MOSFETs de SiC e IGBTs que inclui geração de tensão negativa, detecção de desativação e UVLO em um pacote de 8 pinos. É um driver ideal para um design compacto.

Informações do Dispositivo

| PARTNUMBER | Pacote | Embalagem | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP) | Fita e Bobina | ||||||||||||||||||

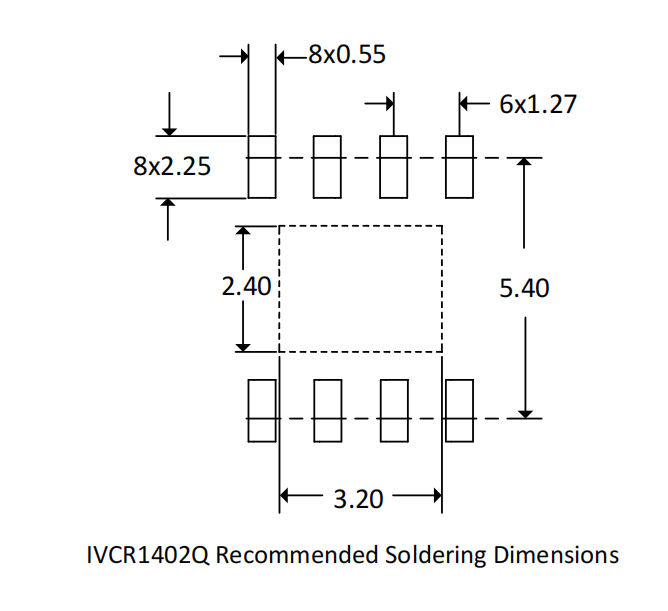

4. Configuração de Pinos e Funções

| pin | Nome | A/O | Descrição | |||||||||||||||||||||||||||||||||||||||||

| 1 | em | Eu | Entrada lógica | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | o | Saída de 5V/10mA para circuito externo | |||||||||||||||||||||||||||||||||||||||||

| 3 | /FAULT | o | Saída de falha de coletor aberto, puxada para baixo quando sobrecorrente ou UVLO for detectado. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | Eu | Entrada de detecção de desatuação | |||||||||||||||||||||||||||||||||||||||||

| 5 | CCC | P | Fonte de alimentação com polarização positiva | |||||||||||||||||||||||||||||||||||||||||

| 6 | - Não. | o | Saída do driver de porta | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | g | Terra do driver | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | o | Saída de tensão negativa | |||||||||||||||||||||||||||||||||||||||||

| Pino exposto | O pino inferior exposto geralmente é conectado ao GND no layout. | |||||||||||||||||||||||||||||||||||||||||||

5. Especificações

5.1 Classificações Máximas Absolutas

Sobre a faixa de temperatura do ar livre (a menos que outra coisa seja especificada) (1)

| mín máximo | unidade | ||||||||||||||||||||||||||||||||||||||||||

| Tensão de alimentação total VCC (referência em relação a GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| VOUT Tensão de saída do driver de porta | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH Corrente de origem de saída do driver de porta (com largura de pulso máximo de 10us e ciclo de trabalho de 0,2%) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| IOUTL Corrente de drenagem de saída do driver de porta (com largura de pulso máximo de 10us e ciclo de trabalho de 0,2%) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| VIN Tensão do sinal de entrada IN | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF Corrente de saída do 5VREF | 25 | Mãe! | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Tensão no DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| Tensão VNEG no pino NEG | OUT-5,0 VCC+0,3 | V | |||||||||||||||||||||||||||||||||||||||||

| Temperatura da junção | -40 150 | °C | |||||||||||||||||||||||||||||||||||||||||

| Temperatura de armazenamento | -65 150 | °C | |||||||||||||||||||||||||||||||||||||||||

(1) Operar além dos valores listados nas Classificações Máximas Absolutas pode causar danos permanentes ao dispositivo.

Exposição por períodos prolongados às condições de classificação máxima absoluta pode afetar a confiabilidade do dispositivo.

5,2 Classificação ESD

| valor | unidade | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Descarga eletrostática | Modelo de corpo humano (HBM), conforme AEC Q100-002 | +/-2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Modelo de dispositivo carregado (CDM), conforme AEC Q100-011 | +/-500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 Condições de Operação Recomendadas

| min | max | unidade | ||||||||||||||||||||||||||||||||||||||||||

| Tensão de alimentação total VCC (referência em relação a GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| VIN Tensão de entrada do gate | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Tensão no DESAT | 0 | CCC | V | |||||||||||||||||||||||||||||||||||||||||

| TAMB Temperatura ambiente | -40 | 125 | °C | |||||||||||||||||||||||||||||||||||||||||

5.4 Informações Térmicas

| IVCR1402DPQR | unidade | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Junção-a-Ambiente | 39 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Junção-para-PCB | 11 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJP Junção-para-pad exposto | 5.1 | °C/W | |||||||||||||||||||||||||||||||||||||||||

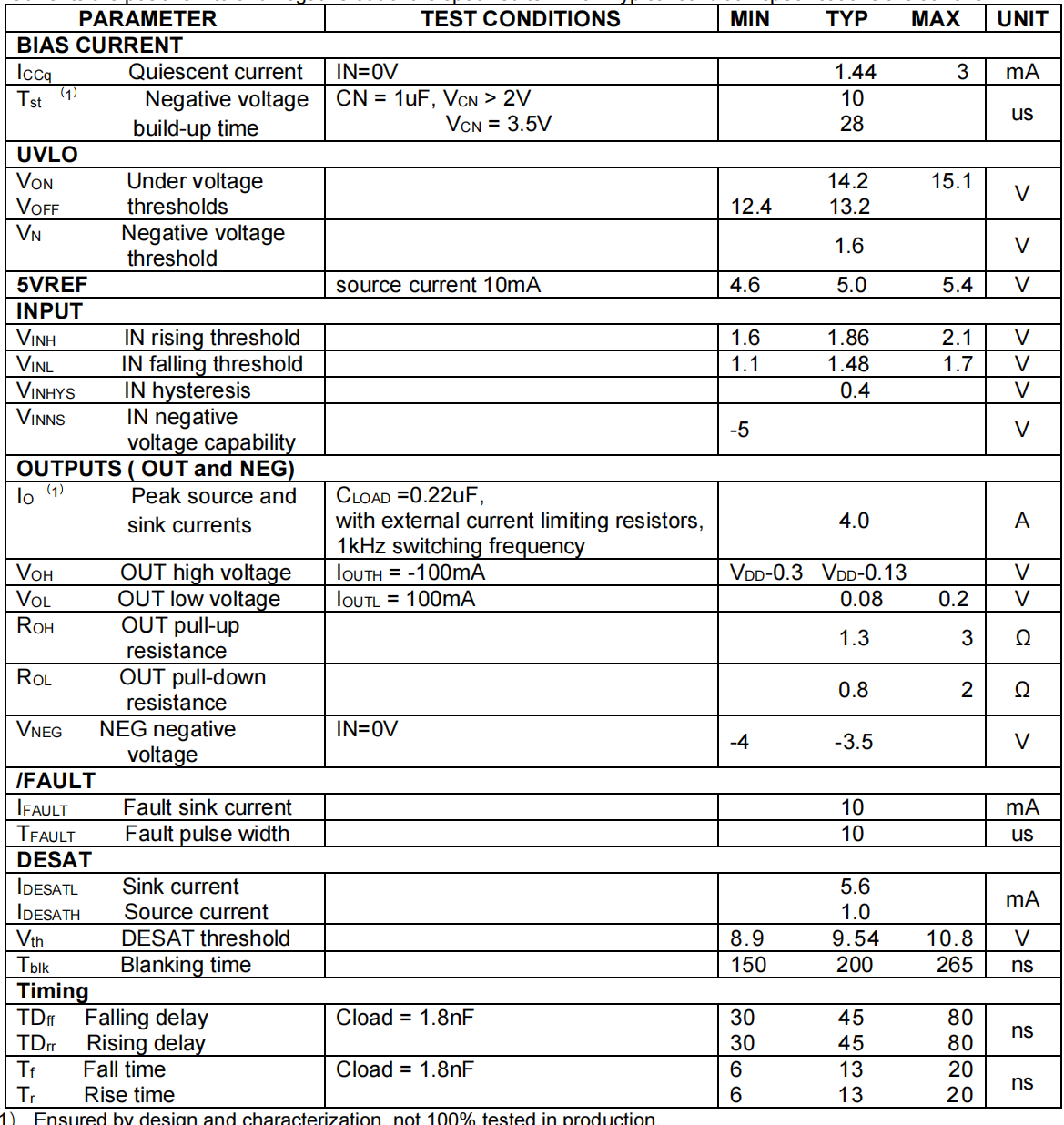

5.5 Especificações Elétricas

A menos que especificado de outra forma, VCC = 25 V, TA = –40°C a 125°C, capacitância de bypass de 1 μF de VCC para GND, f = 100 kHz.

Correntes são positivas na entrada e negativas na saída do terminal especificado. As especificações em condições típicas são a 25°C.

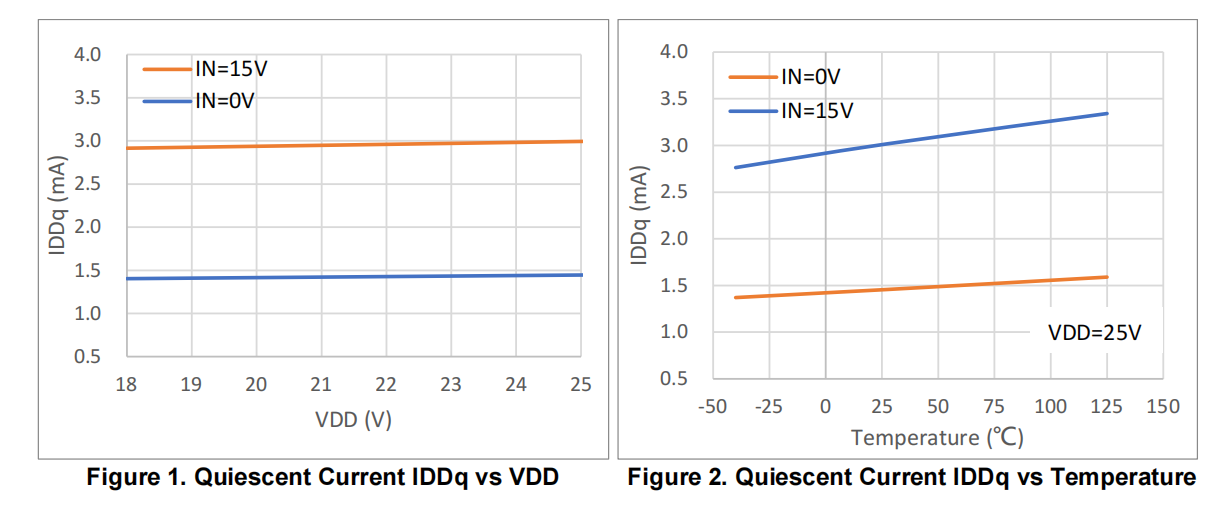

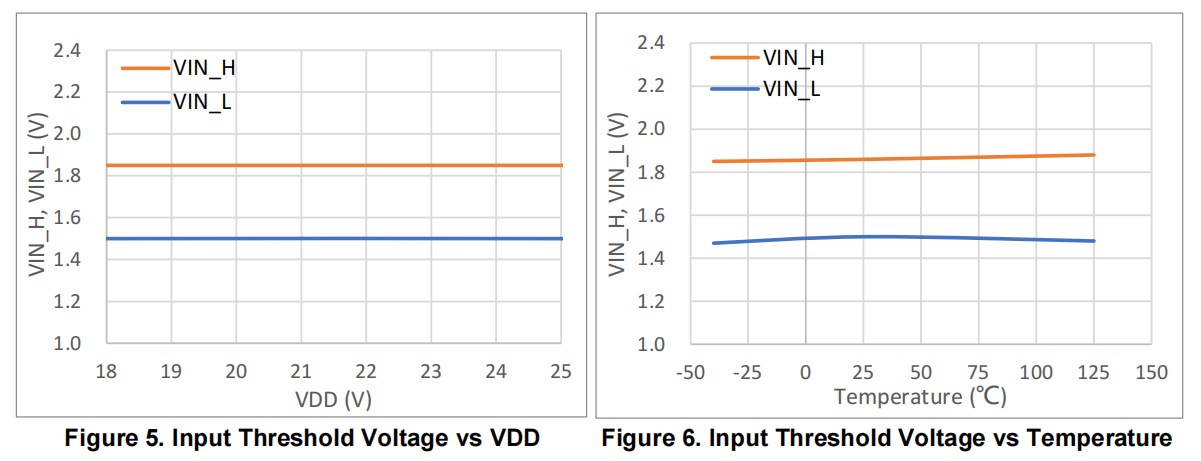

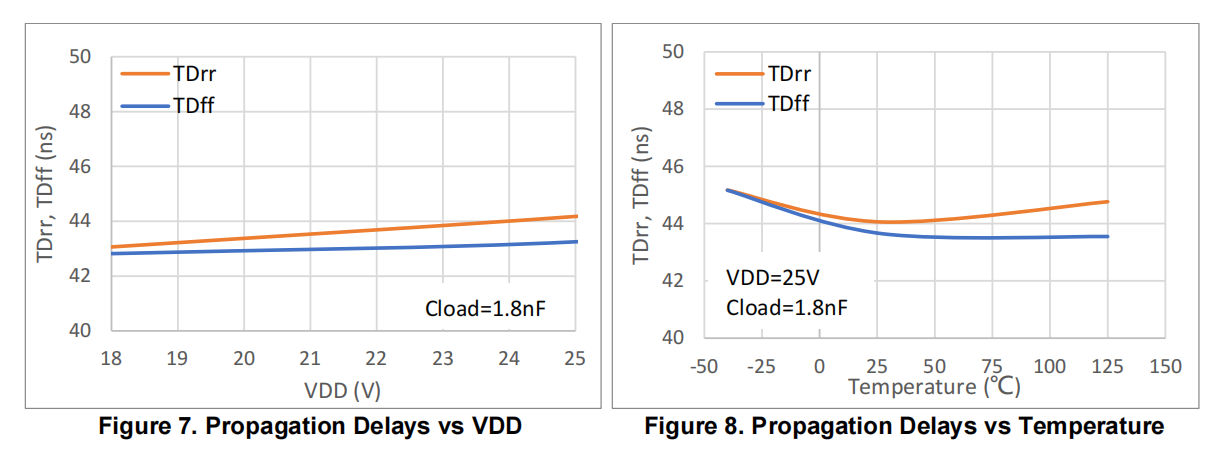

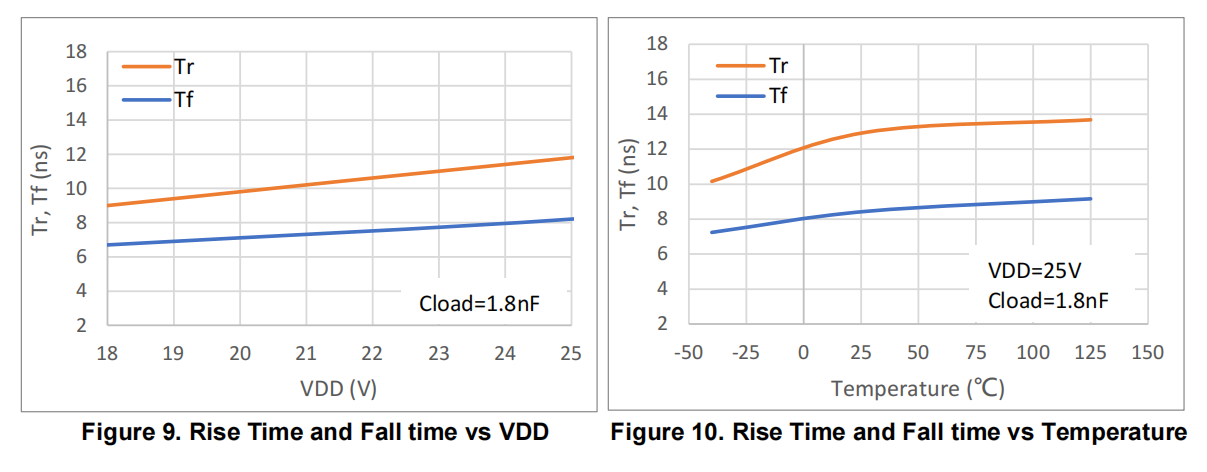

6 Características Típicas

7 Descrição Detalhada

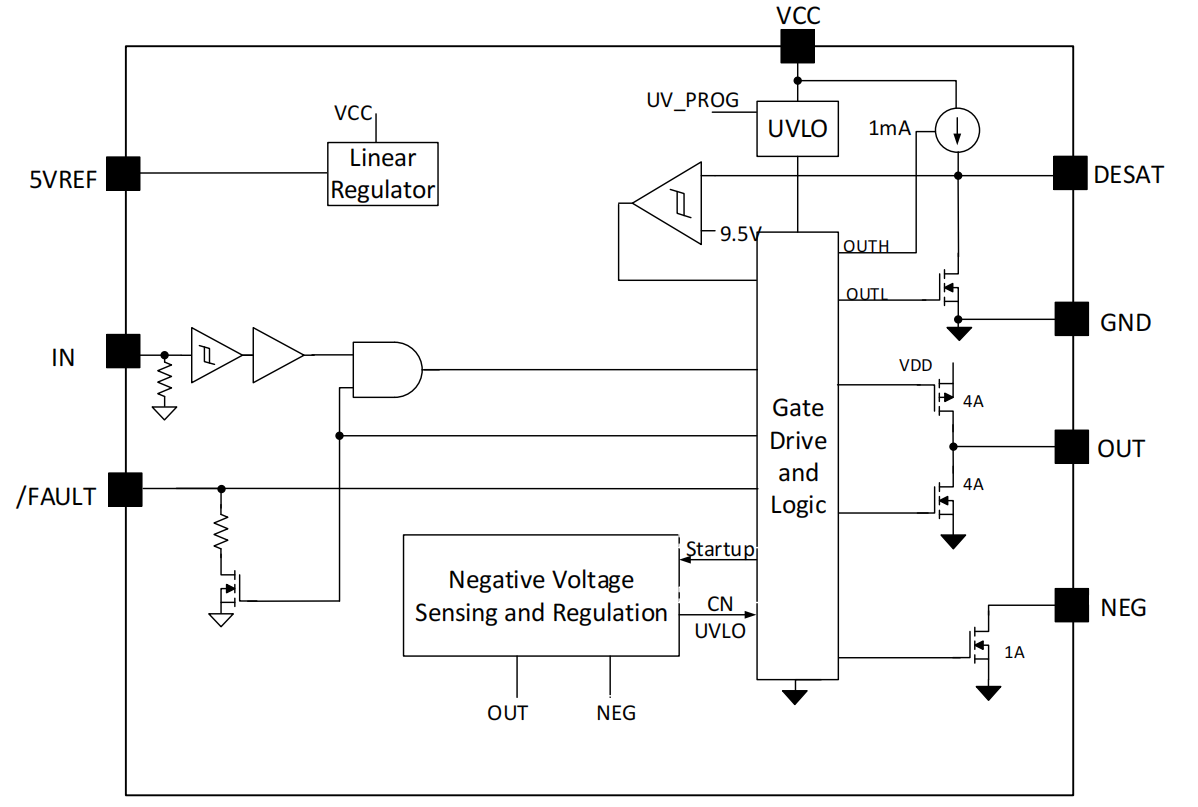

O driver IVCR1402Q representa o avanço mais recente da InventChip em tecnologia de driver de porta de alta velocidade de um único canal de lado baixo.

Ele possui geração interna de tensão negativa, proteção contra saturação/falta de curto-circuito,

UVLO programável. Este driver oferece as características mais avançadas da classe e o design mais compacto e confiável.

Controle de condução do gate do SiC MOSFET. É o primeiro driver da indústria equipado com todas as funções necessárias para condução do gate do SiC MOSFET em um pacote SOIC-8.

com características de condução do gate do SiC MOSFET em um pacote SOIC-8.

Diagrama de Bloco Funcional

7.1 Entrada

IN é uma entrada de driver lógico não inversor. O pino possui um resistor de pull-down fraco. A entrada é compatível com níveis lógicos TTL e CMOS, com tolerância máxima de 20V na entrada.

compatível com níveis lógicos TTL e CMOS, com tolerância máxima de 20V na entrada.

7.2 Saída

IVCR1402Q apresenta uma saída tipo totem-pole de 4A. Ele fornece alta corrente de fonte no momento em que é mais necessário durante a região de platô de Miller na transição de ligação do interruptor de potência. Uma forte capacidade de drenagem resulta em

uma impedância de pull-down muito baixa na etapa de saída do driver, melhorando a imunidade contra o efeito parasita de Miller.

uma muito baixa impedância de pull-down na etapa de saída do driver, melhorando a imunidade contra o efeito parasita de Miller

efeito de ligação, especialmente onde MOSFETs Si de carga de porta baixa ou emergentes MOSFETs de banda larga SiC são

usados.

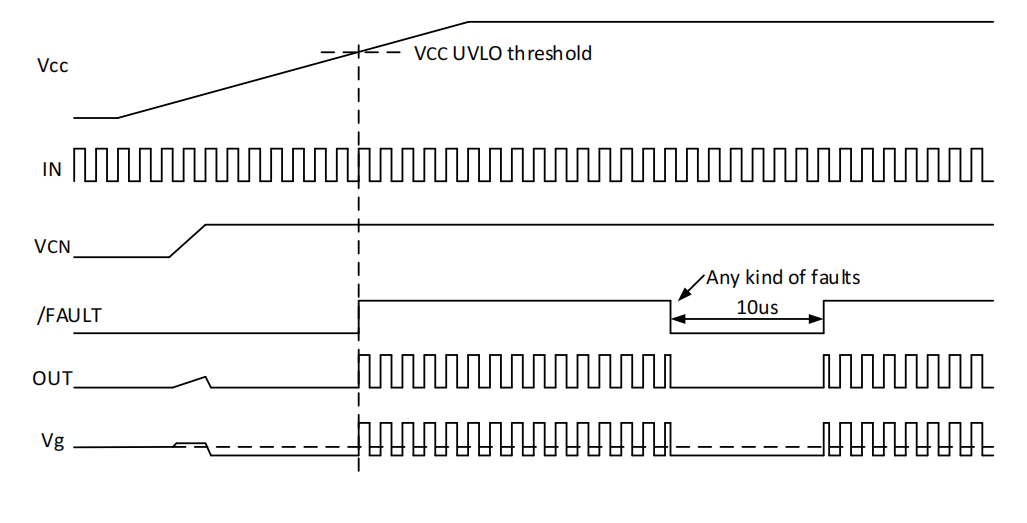

7.3 Geração de Voltagem Negativa

Na inicialização, a saída NEG é puxada para GND e fornece um caminho de alta corrente para uma fonte de corrente carregar o

capacitor de voltagem negativa externo CN (típico 1uF) através da pinça OUT. O capacitor pode ser carregado acima de

2,0V em menos de 10us. Antes que a voltagem do capacitor, VCN, seja carregada, \/FAULT permanece baixa/ativa, ignorando

o nível lógico de IN. Após o viés negativo estar pronto, tanto a pinça NEG quanto a pinça \/FAULT são liberadas e OUT começa a

seguir o sinal de entrada IN. Um regulador de voltagem negativa interno regula a voltagem negativa para -3,5V para operação normal,

independentemente da frequência e ciclo de trabalho PWM. O sinal de condução da porta, NEG, então alterna entre

VCC-3,5V e -3,5V.

7.4 Proteção contra Subtensão

Todos os vieses internos e externos do driver são monitorados para garantir uma condição de operação saudável. O VCC é

monitorado por um circuito de detecção de subtensão. A saída do driver é desligada (puxada para baixo) ou permanece baixa se a

tensão estiver abaixo do limite definido. Note que o limiar de UVLO de VCC é 3,5V maior que as tensões de gate.

A tensão negativa também é monitorada. Seu UVLO possui um limiar fixo de 1,6V em direção negativa. Um defeito no capacitor de tensão negativa pode resultar na tensão do capacitor ficando abaixo do limiar. A proteção UVLO então puxará

o gate do MOSFET para o solo. O sinal \/FAULT é puxado para baixo quando o UVLO é detectado.

Porta do MOSFET conectada ao solo. O \/FAULT é puxado para baixo quando a UVLO é detectada.

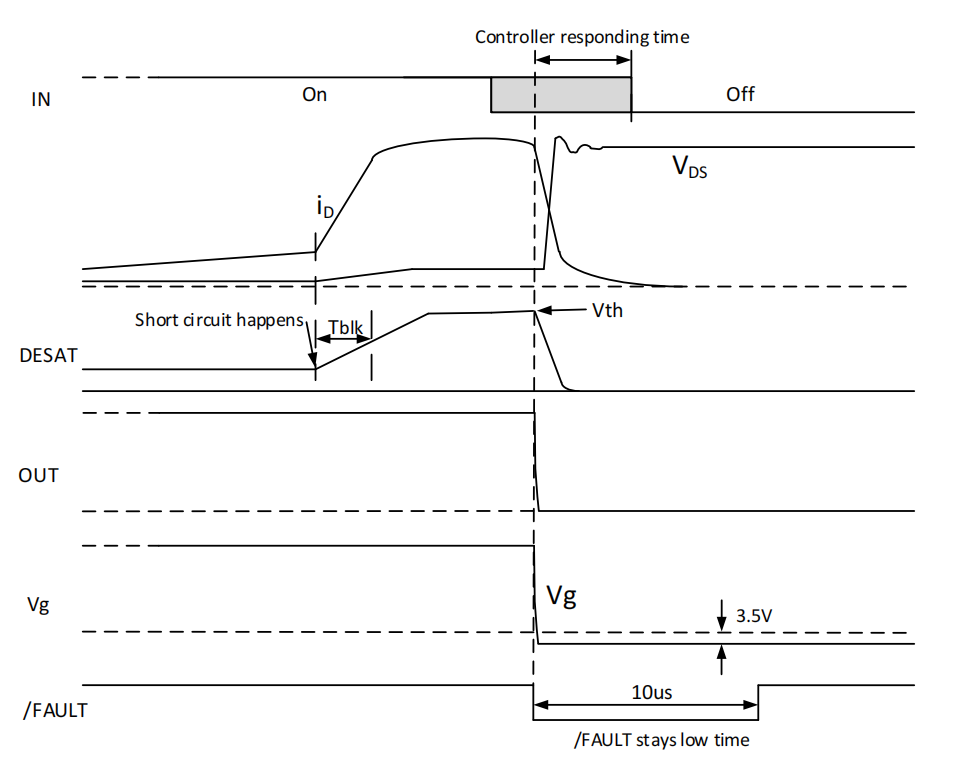

7.5 Detecção de Dessaturação

Quando ocorre curto-circuito ou supercorrente, a corrente do dreno ou coletor do dispositivo de potência (MOSFET de SiC ou IGBT) pode aumentar a tal ponto que o dispositivo sai do estado de saturação, e o Vds\/Vce do

a corrente pode aumentar a um valor tão alto que os dispositivos saem do estado de saturação, e Vds\/Vce do

os dispositivos aumentarão para um valor substancialmente alto. O pino DESAT, com um capacitor de bloqueio Cblk, geralmente limitado a

Id x Rds_on, agora pode ser carregado muito mais alto por uma fonte de corrente constante interna de 1mA. Quando o

tensão atingir o limiar típico de 9,5V, OUT e \/FAULT são ambos levados a baixo. Um tempo de bloqueio de 200ns é inserido

na borda de subida de OUT para evitar que o circuito de proteção DESAT seja acionado prematuramente devido à descarga de Coss.

Para minimizar a perda da fonte de corrente constante interna, a fonte de corrente é desligada quando o interruptor principal

está no estado desligado. Ao selecionar uma capacitância diferente, o tempo de atraso de desligamento (tempo de bloqueio externo) pode ser

programado. O tempo de bloqueio pode ser calculado com

Teblk = Cblk ∙Vth ∕ IDESAT

Por exemplo, se Cblk for 47pF, Teblk = 47pF ∙9,5V ∕ 1mA = 446ns.

Observe que Teblk já inclui o tempo de bloqueio interno Tblk de 200ns.

Para a configuração do limite de corrente, a seguinte equação pode ser usada,

Ilimit = (Vth – R1* IDESAT – VF_D1)\/ Rds_on

onde R1 é um resistor de programação, VF_D1 é a tensão direta do diodo de alta voltagem, Rds_on é a resistência de ligação do SiC MOSFET

na temperatura estimada do junção, como 175C.

Um sistema de energia diferente geralmente requer um tempo de desligamento diferente. Um tempo de desligamento otimizado pode maximizar

a capacidade de curto-circuito do sistema enquanto limita Vds e a oscilação da tensão do barramento.

7.6 Falha

\/FAULT é uma saída de coletor aberto sem resistência de pull-up interna. Quando a dessaturação e as sub-tensões

são detectadas, o pino \/FAULT e OUT são ambos levados ao nível baixo. O sinal \/FAULT permanecerá em nível baixo por 10us após

a condição de falha ser removida. \/FAULT é um sinal de recuperação automática. O controlador do sistema precisará decidir como

para responder ao sinal /FAULT. O diagrama a seguir mostra a sequência de sinais.

7.7 NEG

O capacitor de polarização negativo externo é rapidamente carregado quando NEG fica em nível baixo. Isso ocorre durante a inicialização

e o período de reinicialização, logo antes do período de 10us /FAULT em nível baixo expirar após qualquer falha ser detectada. Durante a inicialização

e o período de reinicialização, a tensão do capacitor de polarização negativa VCN é medida. Assim que a tensão ultrapassa o limiar VN

UVLO, NEG se torna de alta impedância e OUT assume o controle da condução do gate.

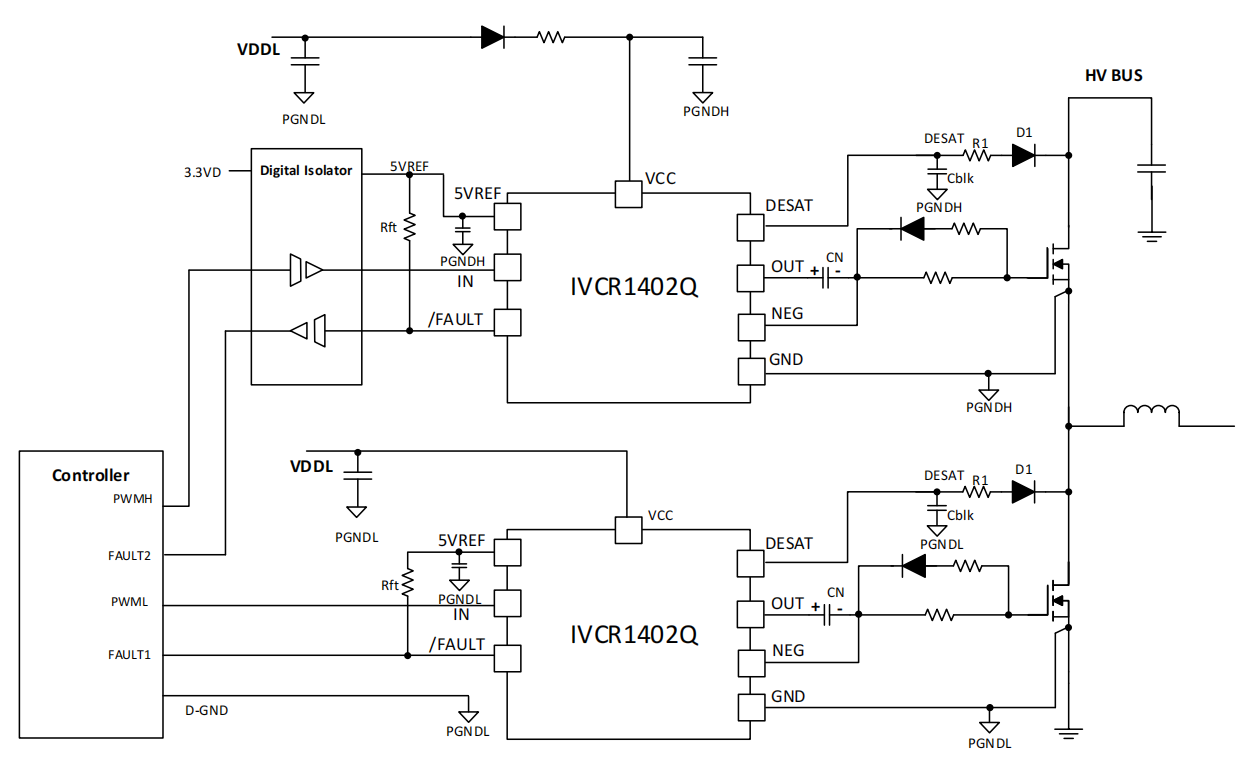

8 Aplicações e Implementação

IVCR1402Q é um driver ideal para um design compacto. É um driver de lado baixo. No entanto, com um gerador de tensão negativa integrado,

o driver pode ser usado como driver de lado alto sem usar um viés isolado.

Então, pode-se usar um bootstrap de baixo custo. O diagrama de circuito a seguir mostra uma ponte-half típica

aplicativo do motorista.

9 Layout

Um bom layout é um passo fundamental para alcançar o desempenho desejado do circuito. O solo sólido é o primeiro a começar com.

Recomenda-se conectar o pino exposto ao solo do driver. É uma regra geral que capacitores têm

uma prioridade maior do que resistores na disposição de localização. Um capacitor de 1uF e um capacitor de decuplagem de 0,1uF

devem estar próximos ao pino VCC e conectados ao plano de terra do driver. O capacitor de tensão negativa deve

estar localizado próximo aos pinos OUT e NEG. O capacitor de bloqueio deve estar próximo ao driver também. Um pequeno filtro

(com constante de tempo de 10ns) pode ser necessário na entrada de IN se as trilhas do sinal de entrada tiverem que passar

por áreas ruidosas. A seguir está um layout recomendado.

10 Informações de Embalagem

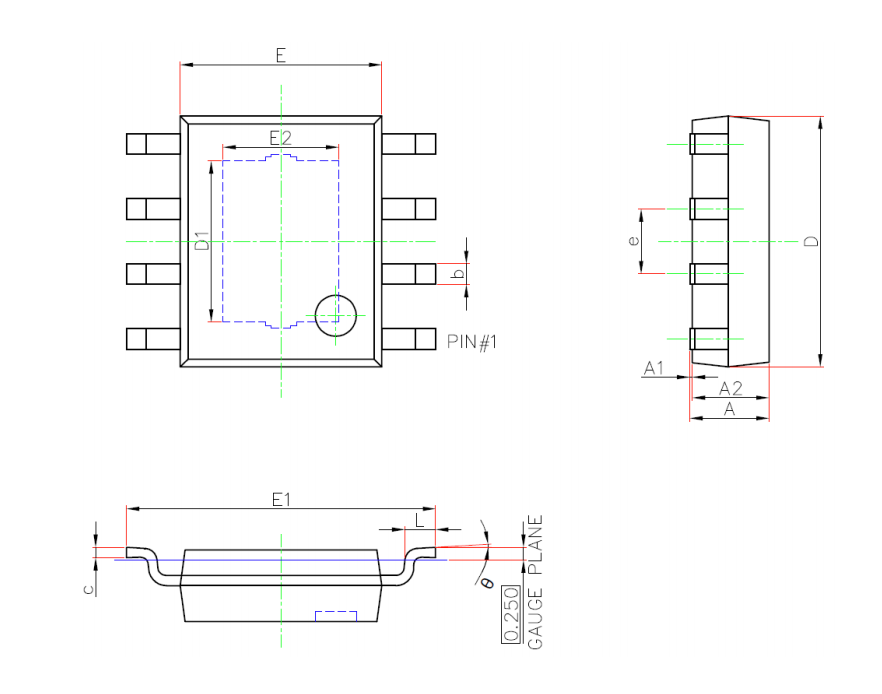

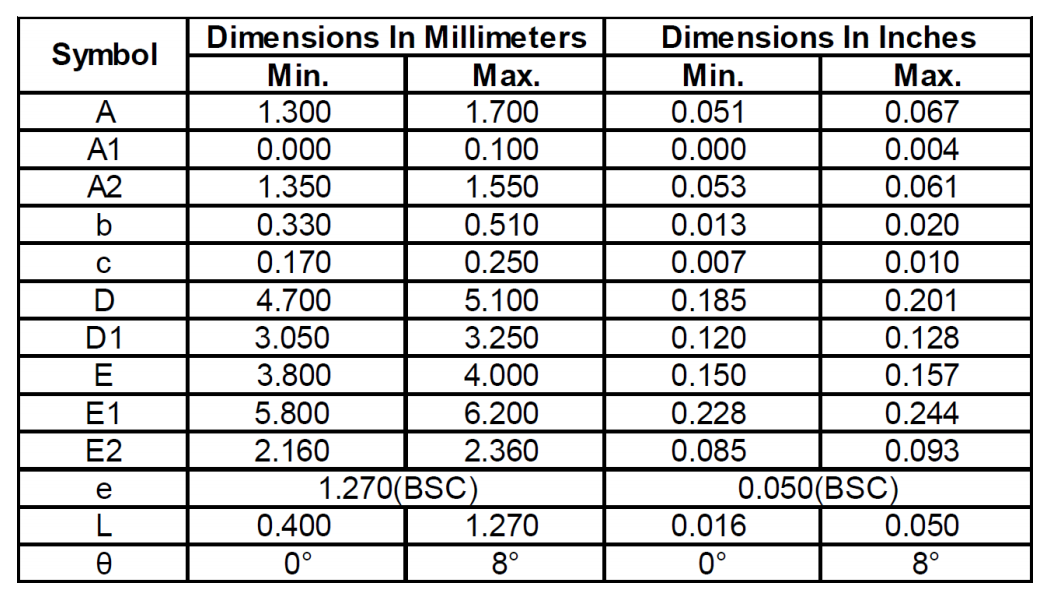

Dimensões do Pacote SOIC-8 (EP)