domum / Products / Components / Porta Coegi

| Locus Origin: | Zhejiang |

| Notam nomen: | Inventchip Technology |

| Model Number: | IVCR1402DPQR |

| Certification: | AEC-Q100 quid |

1. Features

• Coegi current facultatem: 4A submersa et fons apicem coegi current

• Lata VCC vagarentur usque ad 35V

• Integrated 3.5V Praeiudicia negativa

• Designed for low side and suitable for bootstrap high-part power

• UVLO ad positivum et negativum porta coegi voltage

• Desaturation deprehensio pro brevi circuitione tutelae cum internis blanking tempore

• Grand output cum UVLO vel DESAT detectum

• 5V 10mA referentia ad ambitum externum, eg digitalis isolator .

• TTL et CMOS compatible input

• SOIC-8 cum expositis codex frequentia et potentia applicationes

• Minimum propagationis mora 45ns typicam cum aedificare-in de-glitch filter

• AEC-Q100

2. Applications

• EV On Board Scutariorum

• EV/HEV inverters et stationes incurrentes

• AC/DC et DC/DC converters

• Motor Drive

3. Description

IVCR1402Q est AEC-Q100 idoneus, 4A una-alveus, summus celeritatis agitator callidi, potens efficaciter et tuto pulsis SiC MOSFETs et IGBTs. Fortis coegi cum indiligentiis strepitum immunitatis contra Miller effectus in operatione alta dv/dt melioris emendat. Desaturatio detectio deprehensio tutelae ambitus brevem robustam praebet et periculum potentiae fabrica et ratio damnum componentis minuit. Tempus certum 200ns blank inseritur, ne praesidio supercurrente, ne praemature moveatur, mutandi clavum et sonum ore currente. Porta positiva fixa voltage UVLO agitant et fixa custodia negativa UVLO operationem portae sanae voltages efficit. Activum flagitium humilitatis signum est ratio summis montibus cum UVLO vel super current accidit. Minimum propagationis morae ac mis match cum codex scelerisque exposito dat SiC MOSFETs mutandi in centena kHz. Generationem intentionis negativae integrae et 5V referentiae output minimize comitem externam componentis. Prima est agitator industrialis SiC MOSFET et IGBT quae generationis intentionis negativae, desaturationis et UVLO in sarcina 8-pinnarum includit. Est specimen coegi pro pacto consilio.

Information fabrica

| PARTNUMBER | FASCICULUS | COLLYRIOLUM | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP). | Tape et Reel | ||||||||||||||||||

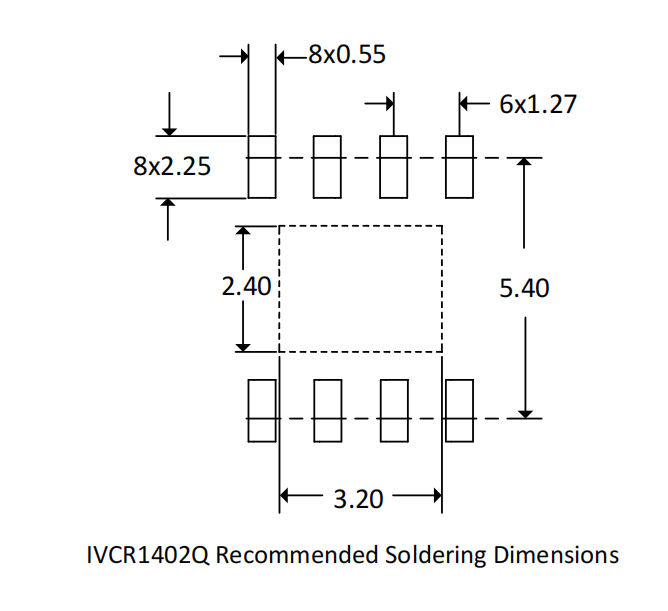

4. Pin configurationis et functiones

| ADFIGO | NOMEN | I / O | DESCRIPTIO | |||||||||||||||||||||||||||||||||||||||||

| 1 | IN | I | Logica input | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | O | 5V/10mA output in circuitu externo | |||||||||||||||||||||||||||||||||||||||||

| 3 | /CULPAM | O | Apertum publicanorum culpae output, cum super current orUVLO deprehenditur, ad depressionem trahi. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | I | Desaturation deprehensio initus | |||||||||||||||||||||||||||||||||||||||||

| 5 | VCC | P | Positivum pondus copia | |||||||||||||||||||||||||||||||||||||||||

| 6 | FORIS | O | Porta exactoris output | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | G | Coegi terram | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | O | Negans voltage output | |||||||||||||||||||||||||||||||||||||||||

| Codex patere | Imo codex expositus saepe cum GND in layout est ligatus. | |||||||||||||||||||||||||||||||||||||||||||

5. cubits

5.1 absolutum Maximum Ratings

Plus libero-aeris temperatus range (nisi aliter notetur) (1)

| MIN MAX | AS | ||||||||||||||||||||||||||||||||||||||||||

| VCC Summa copia voltage (reference to GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| VOUT Gate coegi output voltage | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH Gate coegi output source current (ad max pulsus latitudo 10us et 0.2% officium cycli) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| IOUTL Gate coegi output concidat vena (ad max pulsus latitudo 10us et 0.2% officium cycli) | 6.6 | A | |||||||||||||||||||||||||||||||||||||||||

| VIN IN signo voltage | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF 5VREF output current | 25 | mA | |||||||||||||||||||||||||||||||||||||||||

| VDESAT intentione at DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| VNEG intentione ad NEG pin | OUT-5.0 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| TJ Junction temperatus | -40 150 | ° F | |||||||||||||||||||||||||||||||||||||||||

| TSTG at caliditas | -65 150 | ° F | |||||||||||||||||||||||||||||||||||||||||

(1) Operans ultra eos qui sub Absoluto maximo Rating recensentur, potest detrimentum permanentem machinali inferre.

Patefacio ut condiciones absolutae maximi aestimatae ad tempus protractum afficiat fabrica constantiam.

5.2 ESD Rating

| Value | AS | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Electrostatica missio | Exemplar corporis humani (HBM), per AEC Q100-002 | +/- 2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Praecepit fabrica exemplar (CDM), per AEC Q100-011 | +/- 500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 commendatur Operatio Conditions

| MIN | MAX | AS | ||||||||||||||||||||||||||||||||||||||||||

| VCC Summa copia voltage (reference to GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| VIN Gate input voltage | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT intentione at DESAT | 0 | VCC | V | |||||||||||||||||||||||||||||||||||||||||

| TAMB ambiens temperatus | -40 | 125 | ° F | |||||||||||||||||||||||||||||||||||||||||

5.4 Scelerisque Information

| IVCR1402DPQR | AS | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Junction-ad-Ambient | 39 | F / W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Junctio-ad-PCB | 11 | F / W | |||||||||||||||||||||||||||||||||||||||||

| RθJP expositae adiunctae-ut-codex | 5.1 | F / W | |||||||||||||||||||||||||||||||||||||||||

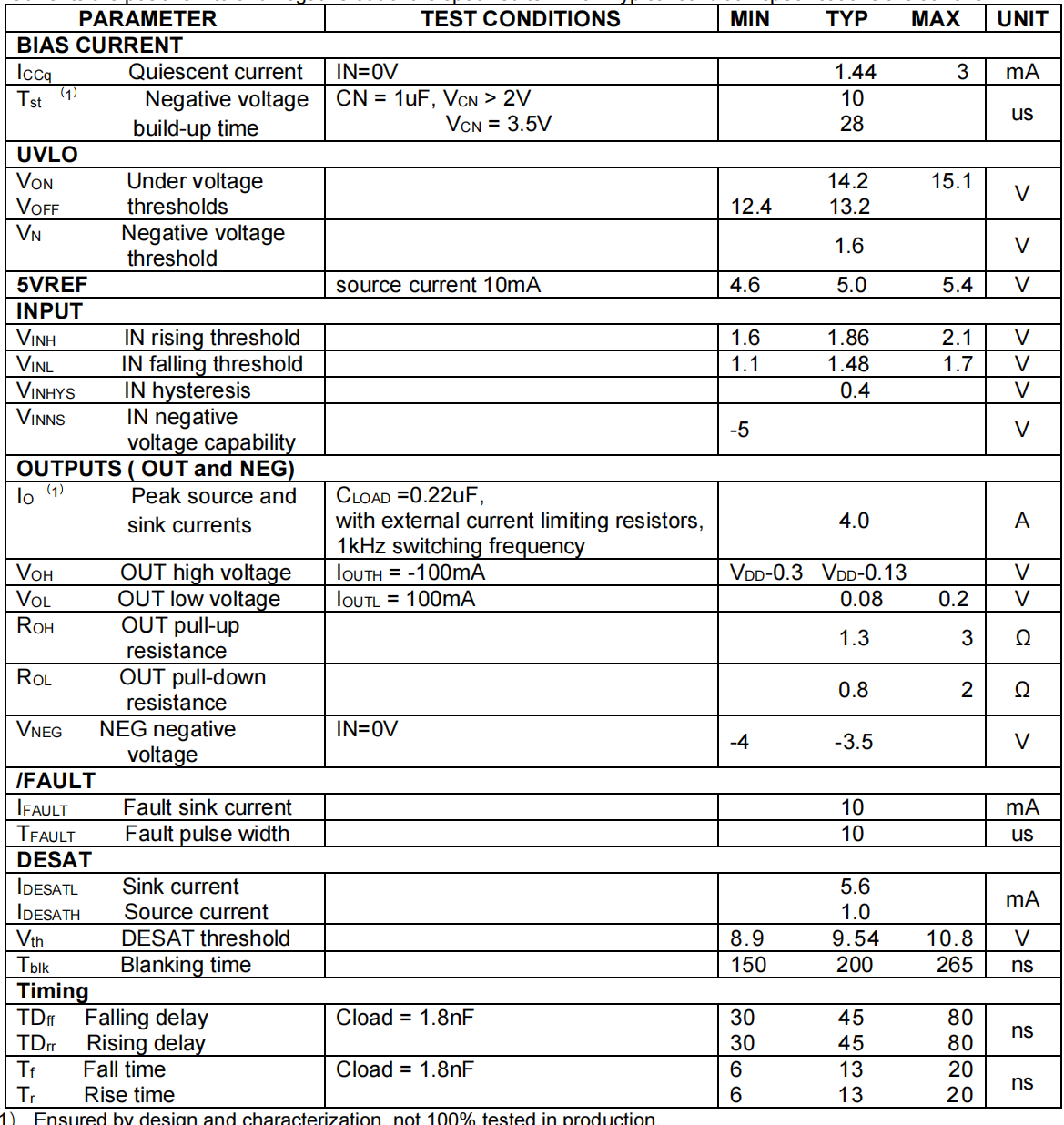

I Electrical Specifications

Nisi aliter notetur, VCC = 25 V, TA = -40°C ad 125°C, 1-μF praetermittant facultatem ab VCC ad GND, f = 100 kHz.

Flumina sunt affirmativa in et negativa ex determinato termino. Specificationes conditionis typicae sunt 25°C.

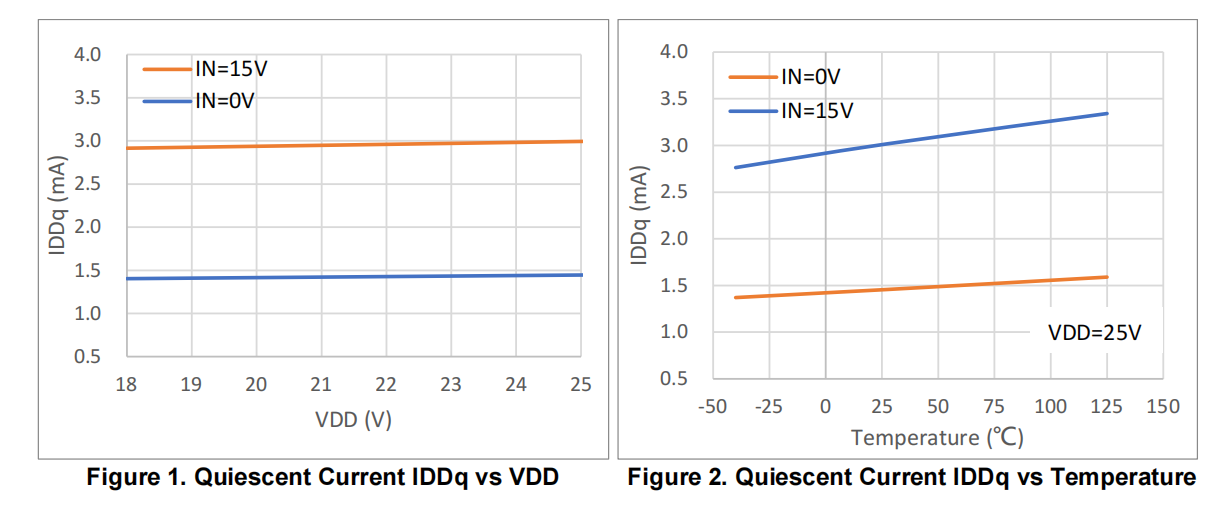

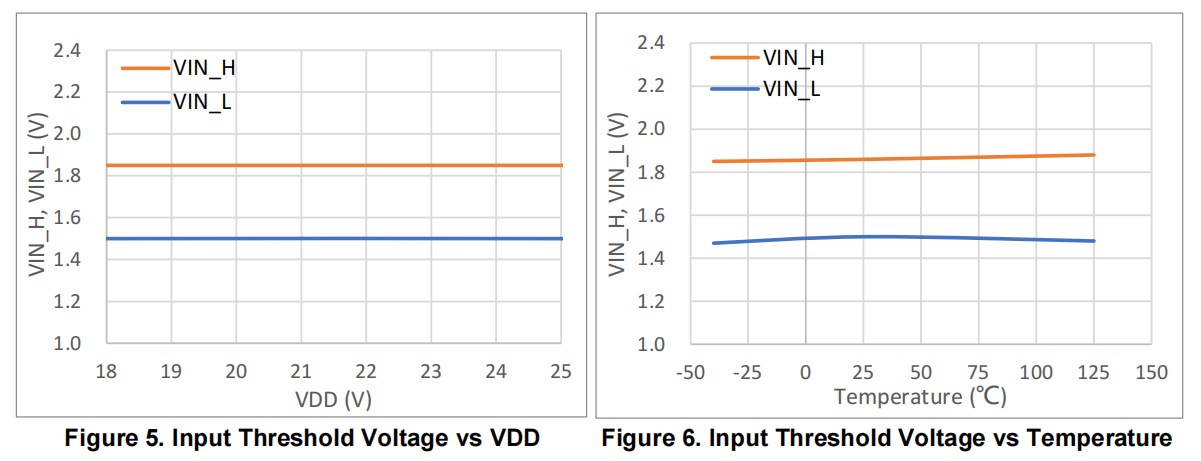

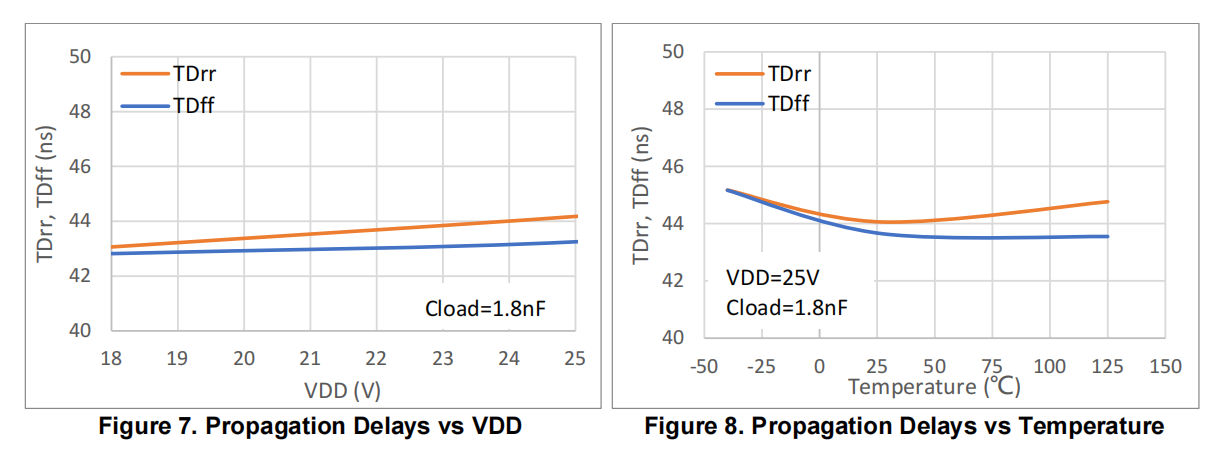

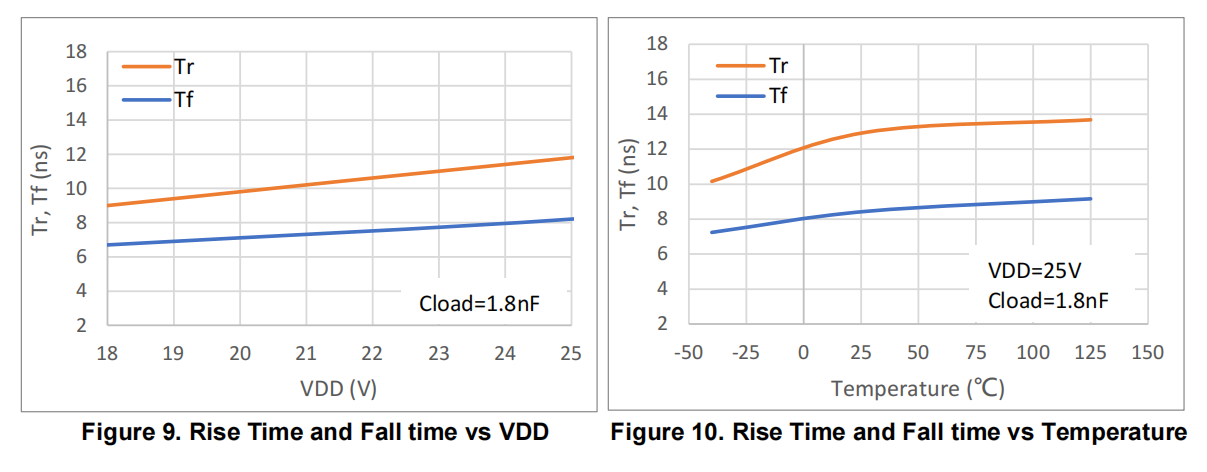

6 Characteres Typici

VII Detail Description

IVCR1402Q exactoris significat InventChip in ore sectionis unius canalis low-parte summus velocitas portae exactoris

technicae progressionis. Lineamenta aedificata in generationis intentione negativa, desaturatione/solutionis tutelae;

programmabilis UVLO. Hoc exactoris praebet optima-in-genus notas ac certissimas et certissimas

SiC MOSFET porta agentes. Prima est industria exactoris omnibus necessariis instructa porta SiC MOSFET

driving features in SOIC-8 sarcina.

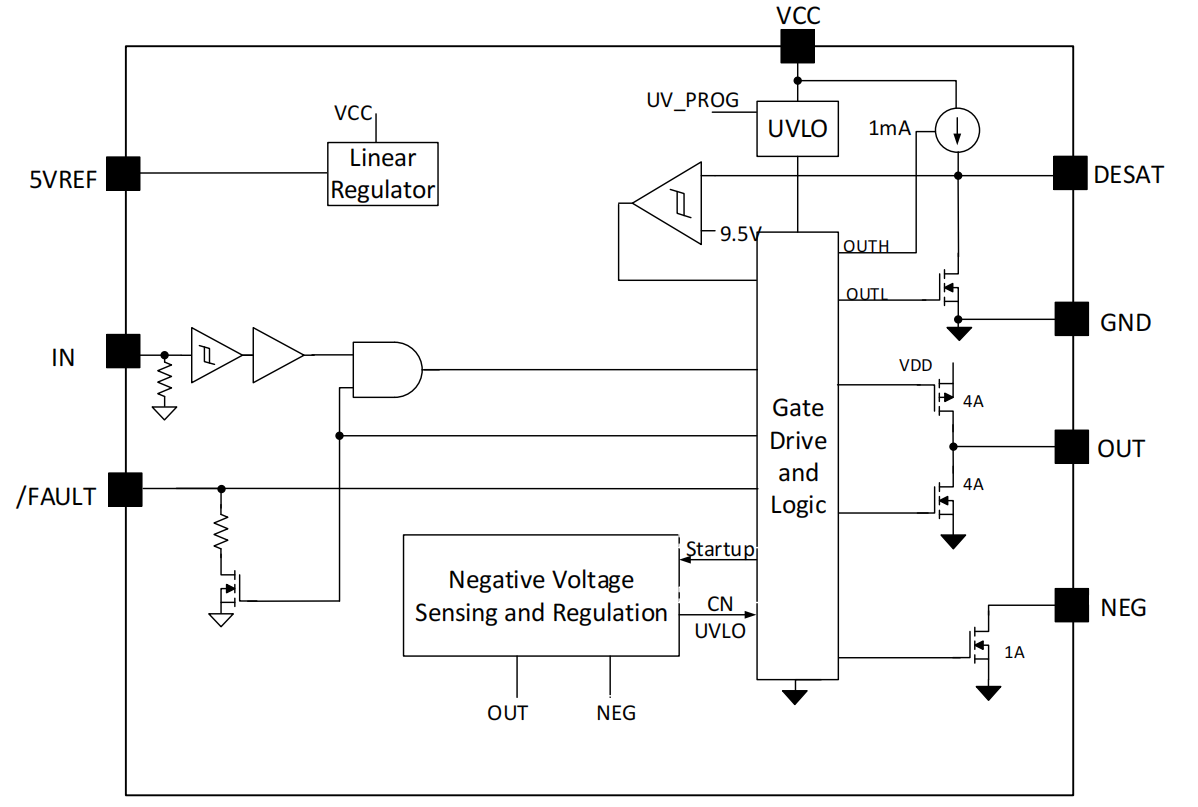

Munus Acta Diagram

III potenti

IN non-invertendo logicam porta ultrices input. Acus infirma pulldown habet. Initus est TTL et CMOS

cum gradu maximo 20V input tolerantiae logicae compatible.

Output 7.2

IVCR1402Q lineamenta 4A totem-pole output scaena. Fontem venam altam tradit, cum maxime est

opus est in regione Miller planitiei potentiae transitum tractum in transitu. Facultas descendendi fortis resultat in

ima viverra-descendit impedimentum in scaena agitatoris output, quae immunitatem contra parasiticam Miller emendat

vertere in effectum, praesertim ubi portae-gravis Si MOSFETs vel late emergentes bandgap SiC MOSFETs sunt

usus est.

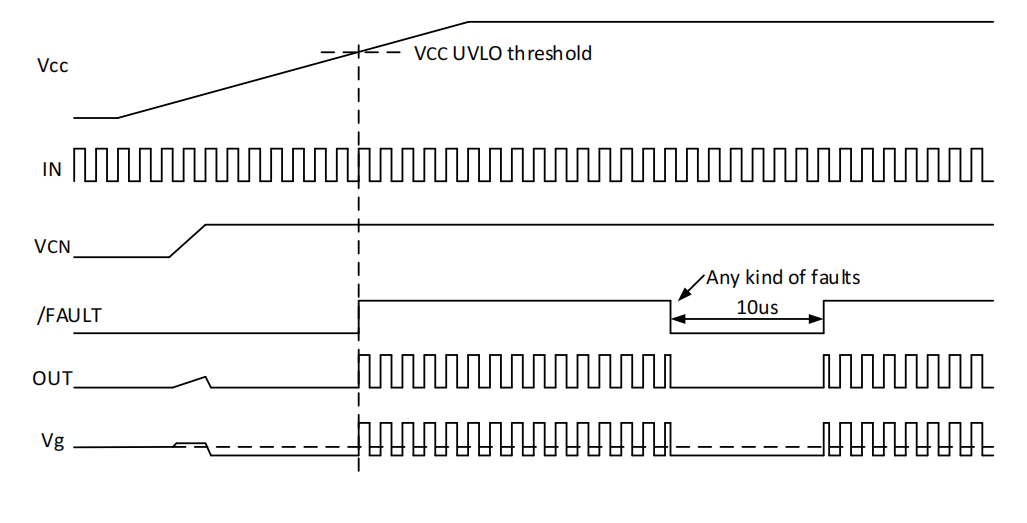

7.3 Negative intentione Generationis

In satus, NEG output ad GND trahitur et altam venam praebet ad fontem currentem qui accusatur

capacitor negativo-voltatio externa CN (1uF typica) per E pin. Capacator potest accusari supra

2.0V intra 10us. Ante intentionem capacitorem, VCN, comminatus est, / MALITIA humilis/activa, neglecta remanet

UT GRATIA LOGICA s. Post Negativa bias parata est, tum NEG clavum et / CULPA clavum emittuntur et E incipit ad

sequitur input signum IN. A aedificato-in intentione negativa ordinator ordinans intentionem negativam ad -3.5V pro normali

operatio, cuiuscumque PWM frequentiae et officii currendi. Porta coegi signum, NEG, deinde permutat

VCC-3.5V et -3.5V.

7.4 sub intentione praesidia

Omnes internae et externae biationes aurigae monitores sunt ad sanam condicionem operationis invigilandam. VCC is

viverra in intentione deprehensio per ambitum. Exactoris output clauditur (humilis) vel humilis remanet si

voltage infra pone modum. Nota quod VCC UVLO limen est 3.5V altior quam porta voltages.

Negativa intentione monitorem quoque adhibet. Eius UVLO fixum 1.6V in limine negativo habet. Negative voltage

capacitor defectus in intentione capacitoris infra limen provenire potuit. UVLO tutela erit tunc trahere

MOSFET porta ad terram. VITIUM humilior cum UVLO deprehenditur.

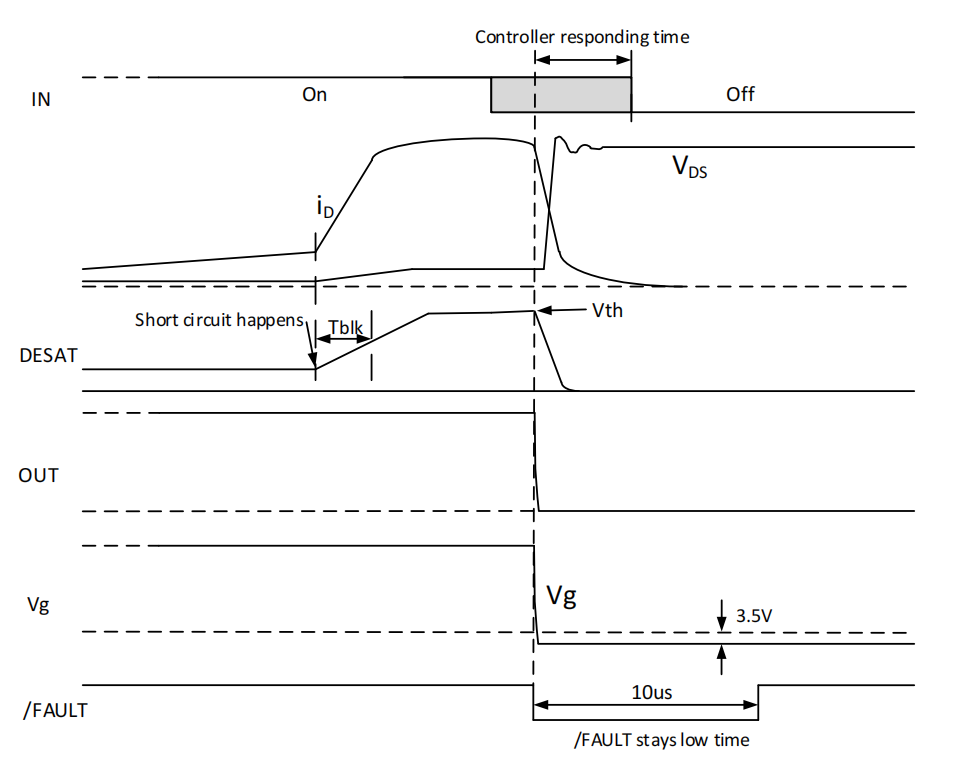

7.5 Desaturation Detection

Cum brevis circuitus vel super current accidit, vis machinae (SiC MOSFET vel IGBT) exhauriunt vel collector

vena augeri potest tam magni pretii ut machinis e statu saturitatis exeant, et Vds/Vce of

cogitationes ascendet ad substantiam contemnendam. DESAT paxillus cum capaci- tate blank, normaliter coagmentatus

Id x Rds_on, nunc multo altius arguere 1mA interno fonte constanti potest. Cum autem

intentione 9.5V limine typicam attingit, EXTRA et / MERITUM utrumque humile trahitur. A 200ns blank tempore inseritur

at in margine EGRESSUS oriatur ne DESAT ambitum protegat ne praemature ob missionem Coss urgeatur.

Ad minuendam perniciem interni fontis qui assidue est, fons hodiernus submovetur cum transitum principale

est procul re publica off. Aliam facultatem eligendo, tempus morae averte (tempus vacua externa) potest esse

programma. Vacuum tempus computari potest;

Teblk = Cblk Vth / IDESAT

Exempli gratia, si Cblk est 47pF, Teblk = 47pF ∙9.5V/1mA = 446ns.

Nota Teblk includit internum Tblk 200ns blank tempus iam.

Ad terminum currenti occasus, sequenti aequatio adhiberi potest;

Ilimit = (Vth - R1* IDESAT - VF_D1)/ Rds_on

ubi R1 programmatio resistor est, VF_D1 est alta intentione diode deinceps intentione, Rds_on est SiC MOSFET tractus

resistentia ad commissuram caliditatis aestimandam, ut 175C.

Alia ratio potentiae plerumque diversum temporis intervallum requirit. An optimized vicis-off potest maximize

systema brevis circuitionis capacitatis dum limitando Vds et bus intentione tinnitus.

7.6 Culpa

/ VITIUM collector aperta est cum resistentia trahere non interna. Cum desaturation et sub voltages

deprehenduntur, / MALITIA paxillus et EGRESSUS utrumque humile trahuntur. In / MERITUM signum erit humilis ad 10us post

culpae conditio tollitur. / MENDUM auto recuperatio signum est. Systema moderatoris opus est decernere quomodo

ad respondendum / MERITUM signum. Sequens tabula signum sequentiam ostendit.

7.7 NEG

Facultas negativa externa cito comminatur, cum NEG humilis accedit. Hoc fit in potentia sursum

et sileo tempus ante 10us / CULPA low periodus exspirat postquam aliqua culpa deprehenditur. Per potentiam

et sileo periodum, capacitor intentionis negativae VCN mensuratur. Ut primum in intentione est ultra VN

UVLO limen, NEG altum fit impedimentum, et porta Eiciam occupat imperium.

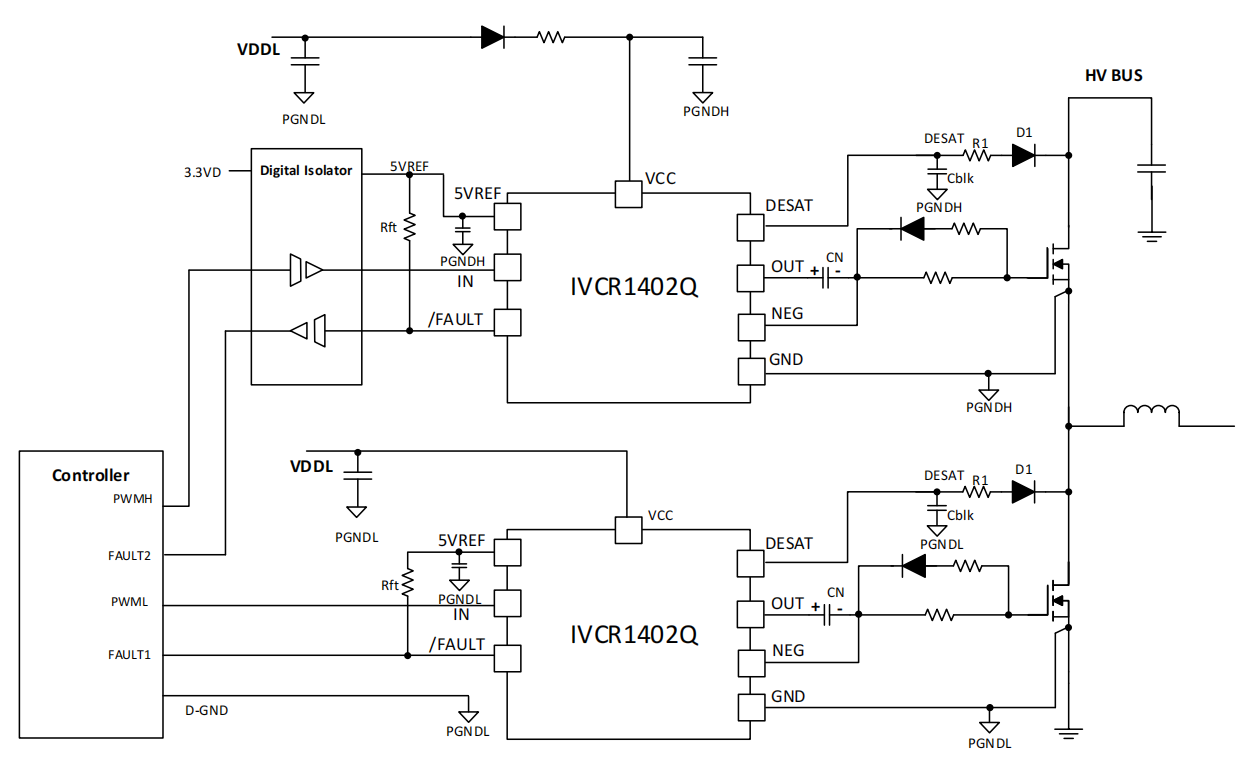

VIII Applications et exsequendam

IVCR1402Q coegi est specimen pro pacto consilio. Humilis latus exactoris est. Sed cum structum-in-

Negative voltage generantis agitator adhiberi potest ut summus latus exactoris absque usu remoto studio.

Humilis sumptus bootstrap tunc loco adhiberi potest. Sequens diagramma dimidium pontis typicam ostendit

exactoris spectat.

9 Layout

Bona propositio clavis est gradus ad perficiendum ambitum desideratum. Prima solida committitur terra.

Commendatur codex aurigae humum ligare expositos. Regula generalis est quam capacitores habent

altioris prioritatis quam resistors ad locum dispositio. A 1uF et 0.1uF decoupling capacitors

sit prope VCC paxillus et exactoris loco plano fundatus. capacitor negans voltage debet

prope ad E and NEG paxillos collocare. Vestis capacitor tum aurigae proximus esse debet. A parva filter

(with10ns time constant) requiri potest ad input of IN, si vestigia initus signa passa sunt

per aliquam multitudinem regio. Suspendisse at arcu est.

10 Packaging Information

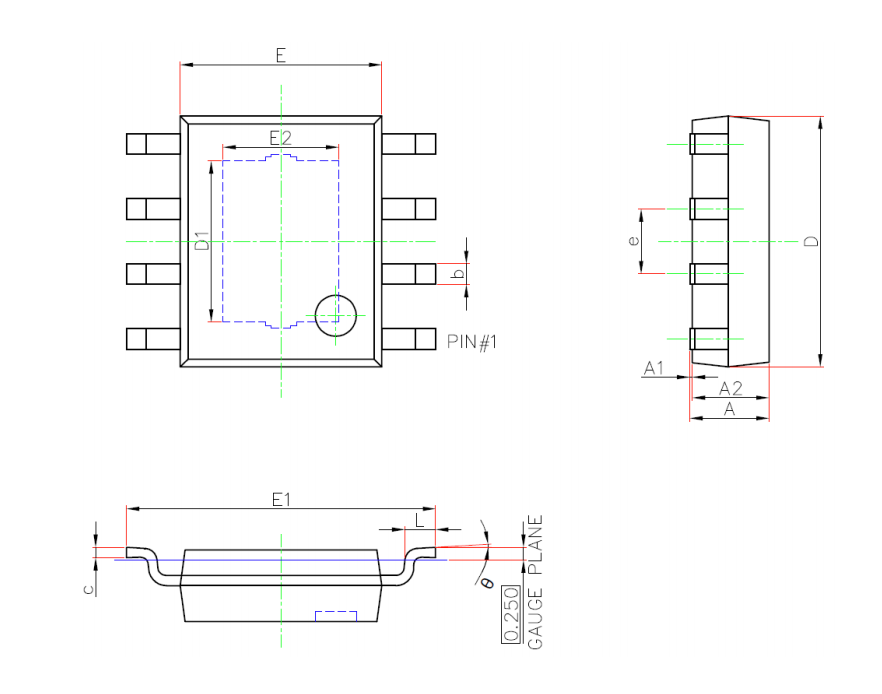

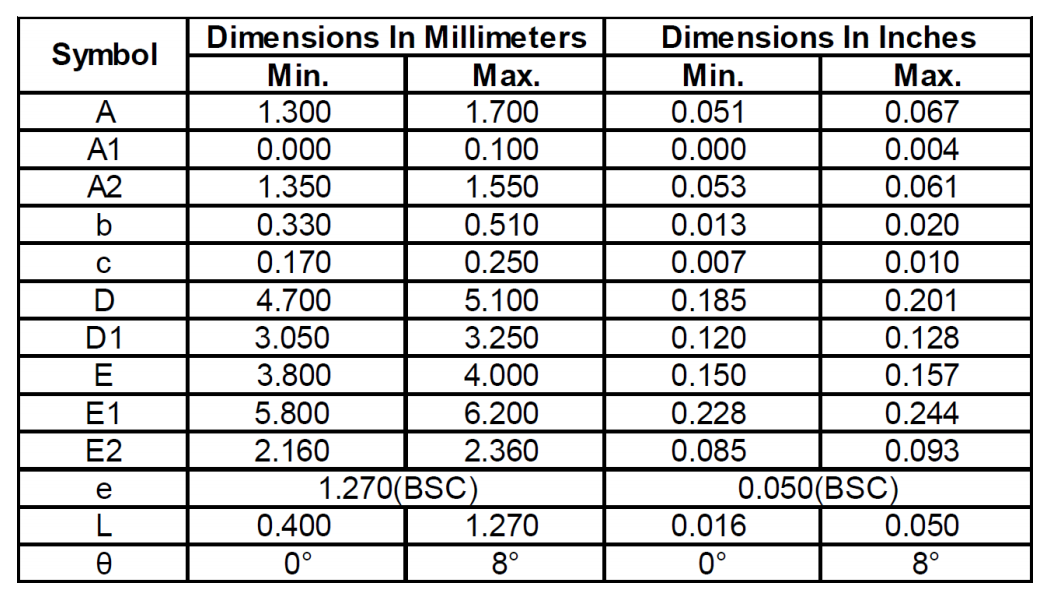

SOIC-VIII (EP) Sarcina Dimensiones