| Mjesto podrijetla: | Zhejiang |

| Naziv marke: | Inventchip Technology |

| Broj modela: | IVCR1402DPQR |

| Certifikacija: | Odobren prema AEC-Q100 |

1. Značajke

• Kapacitet strujnog pogona: 4A sink i izvorišni peek pogonske struje

• Širok opseg VCC do 35V

• Integrirani 3.5V negativni pomak

• Dizajniran za spuštenu stranu i prilagođen bootstrap visokoj strani snage

• UVLO za pozitivan i negativni napetostni pomak za vođenje

• Otkrivanje desaturacije za zaštitu od kratkog spoja s unutrašnjim vremenom isključivanja

• Izlazna pogreška kada je otkrivena UVLO ili DESAT

• 5V 10mA referenca za vanjski krug, npr. digitalni izolator

• Ulaz kompatibilan s TTL i CMOS

• SOIC-8 s otkrivenim padom za aplikacije visoke frekvencije i snage

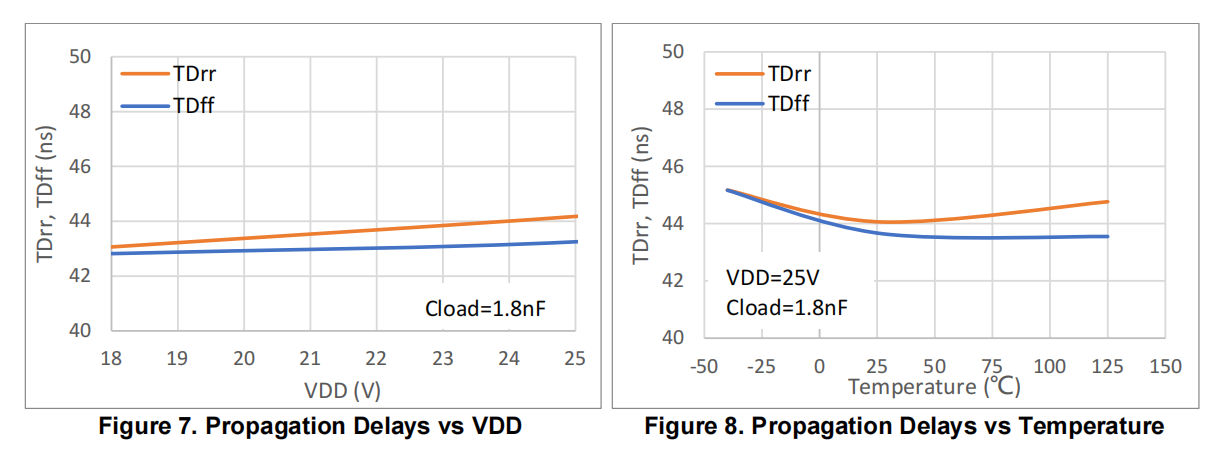

• Niska proporcionalna kašnjenja 45ns tipično sa ugrađenim filterom za eliminaciju šumova

• Kvalificirano prema AEC-Q100

2. Primjene

• Napajanja za ugradbeni punjenje EV

• Inverteri i stanice za punjenje EV/HEV

• Pretvarači AC/DC i DC/DC

• Pogonski sistem

3. Opis

IVCR1402Q je kvalificiran prema AEC-Q100, 4A jednokanalni, brzi pametni vođa, sposoban učinkovito i sigurno upravljati SiC MOSFET-ima i IGBT-ima. Jači vođa s negativnim pomakom poboljšava otpornost na šum uzrokan Miller efektom tijekom visoke brzine promjene napona (dv/dt). Detekcija desaturacije pruža robustnu zaštitu od kratkog spoja i smanjuje rizik oštećenja snaga uređaja i komponenti sustava. Ugrađeno je fiksno vremensko zastojanje od 200ns kako bi se spriječilo prematura aktivacija zaštite od preopterećenja strujom zbog trenutnog povećanja i šuma tijekom prelaznog stanja. Fiksna pozitivna i negativna UVLO zaštita osigurava ispravne radne napone na vrata. Aktivni nizi signal za grešku upozorava sustav kada dođe do UVLO ili preopterećenja strujom. Niska propagacijska kašnjenja i nepodudarnost uz izloženu toplinsku ploču omogućuju SiC MOSFET-ima rad na stotine kHz. Integrirana generacija negativne napaje i 5V referentni izlaz smanjuju broj vanjskih komponenti. To je prvi industrijski vođa za SiC MOSFET-e i IGBT-e koji uključuje generaciju negativne napredne, detekciju desaturacije i UVLO u 8-pin pakiranju. Idealan je vođa za kompaktan dizajn.

Informacije o uređaju

| PARTNUMBER | Pakiranje | Pakiranje | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP) | Ljepenka i bobina | ||||||||||||||||||

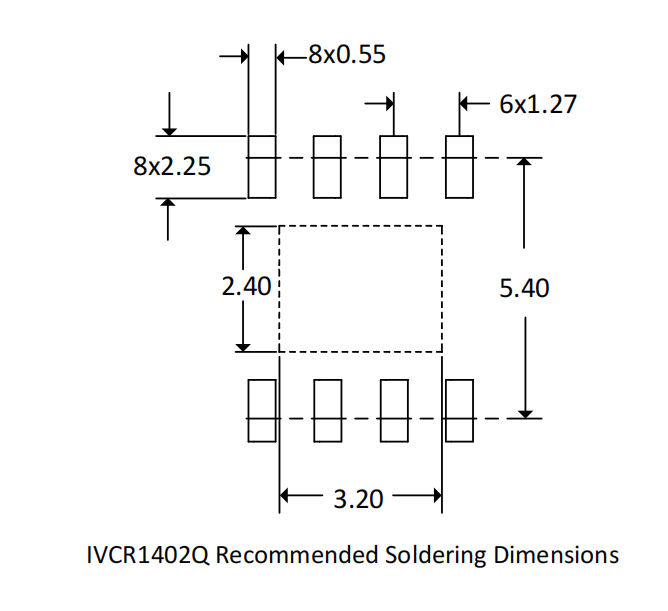

4. Konfiguracija i funkcije pinova

| pin | Naziv | I/O | Opis | |||||||||||||||||||||||||||||||||||||||||

| 1 | u | Ja | Ulaz za logiku | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | O | Izlaz od 5V/10mA za vanjski krug | |||||||||||||||||||||||||||||||||||||||||

| 3 | /FAULT | O | Otvoreni kolektor izlaz za grešku, spušten na nižu ravan kada se otkrije preveliki tok ili UVLO. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | Ja | Ulaz za otkrivanje desaturacije | |||||||||||||||||||||||||||||||||||||||||

| 5 | VCC | P | Pozitivna napajanja | |||||||||||||||||||||||||||||||||||||||||

| 6 | IZLAZ | O | Izlaz vođenja vrata | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | G | Zemlja vođenja | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | O | Izlazni negativni naprez | |||||||||||||||||||||||||||||||||||||||||

| Otkrivena pločica | Donja otkrivena pločica često je spojena na GND u rasporedu. | |||||||||||||||||||||||||||||||||||||||||||

5. Specifikacije

5.1 Apolutno maksimalne vrijednosti

Preko slobodnog temperaturnog raspona (osim ako nije drugačije navedeno) (1)

| min max | Jedinica | ||||||||||||||||||||||||||||||||||||||||||

| Ukupna napajna naprezina VCC (referenca na GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| NAPREŽINA IZLAZA VOUT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH izvorni strujni izlaz drivera vrata (za maksimalnu impulznu širinu 10us i ciklusno vrijeme 0.2%) | 6.6 | A. | |||||||||||||||||||||||||||||||||||||||||

| IOUTL stjecni strujni izlaz drivera vrata (za maksimalnu impulznu širinu 10us i ciklusno vrijeme 0.2%) | 6.6 | A. | |||||||||||||||||||||||||||||||||||||||||

| VIN IN signala naprezina | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF izlazni strujni tok 5VREF | 25 | Ja | |||||||||||||||||||||||||||||||||||||||||

| VDESAT naprezina na DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| VNEG Naprezje na pinu NEG | OUT-5.0 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| TJ Spojna temperatura | -40 150 | °C | |||||||||||||||||||||||||||||||||||||||||

| TSTG Temperatura skladištenja | -65 150 | °C | |||||||||||||||||||||||||||||||||||||||||

(1) Rad izvan granica navedenih kao apsolutno maksimalne ocjene može uzrokovati trajnu štetu uređaju.

Izloženost uvjetima apsolutno maksimalne ocjene u dugu vremenskom razdoblju može utjecati na pouzdanost uređaja.

5.2 Ocijena ESD

| Vrijednost | Jedinica | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Elektrostatičko otpuštanje | Model ljudskega tijela (HBM), po AEC Q100-002 | +/-2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Model napućenog uređaja (CDM), po AEC Q100-011 | +/-500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 Preporučeni uvjeti rada

| min | max | Jedinica | ||||||||||||||||||||||||||||||||||||||||||

| Ukupna napajna naprezina VCC (referenca na GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| VIN Ulazna naprijed za vrata | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT naprezina na DESAT | 0 | VCC | V | |||||||||||||||||||||||||||||||||||||||||

| TAMB Oko okolišne temperature | -40 | 125 | °C | |||||||||||||||||||||||||||||||||||||||||

5.4 Termičke informacije

| IVCR1402DPQR | Jedinica | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Spojnice-do-okoliš | 39 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Spoj-nakon-PCB | 11 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJP Spoj-na-otvorenu pločicu | 5.1 | °C/W | |||||||||||||||||||||||||||||||||||||||||

5.5 Električne specifikacije

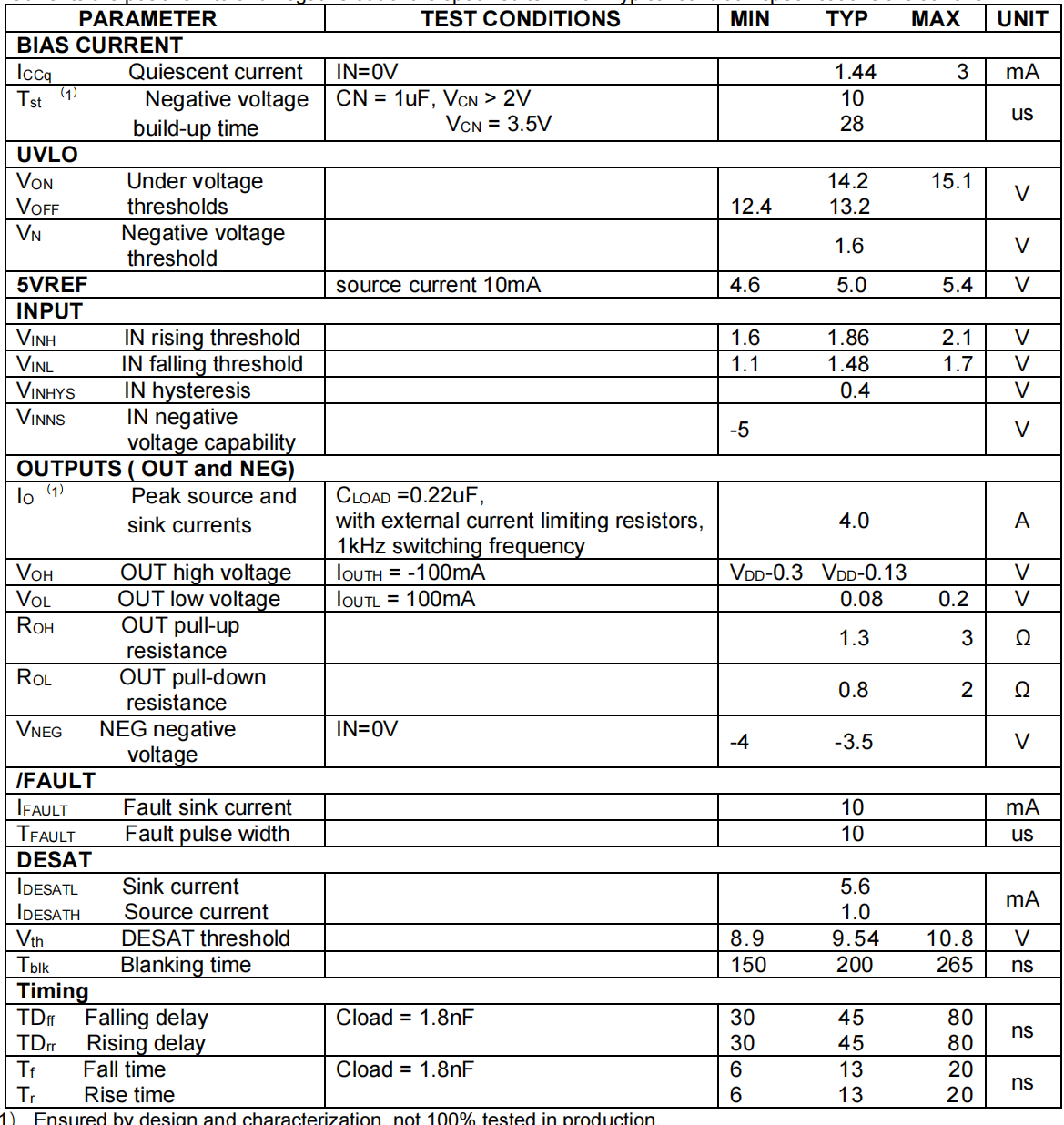

Osim ako nije drugačije navedeno, VCC = 25 V, TA = –40°C do 125°C, 1-μF bypass kondenzator između VCC i GND, f = 100 kHz.

Struje su pozitivne kad ulaze i negative kad izlaze iz određenog terminala. Tipične uvjete specifikacija su pri 25°C.

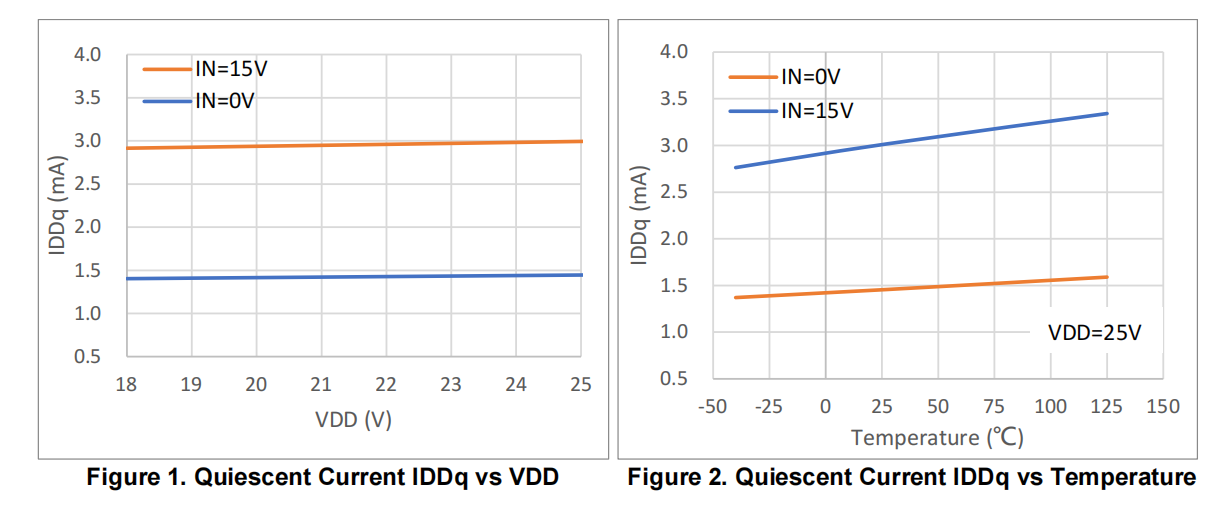

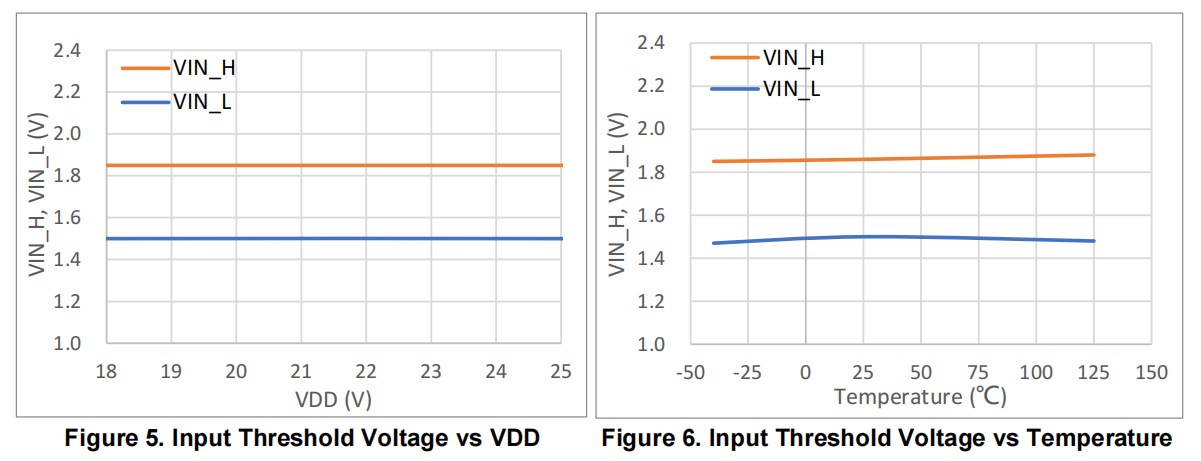

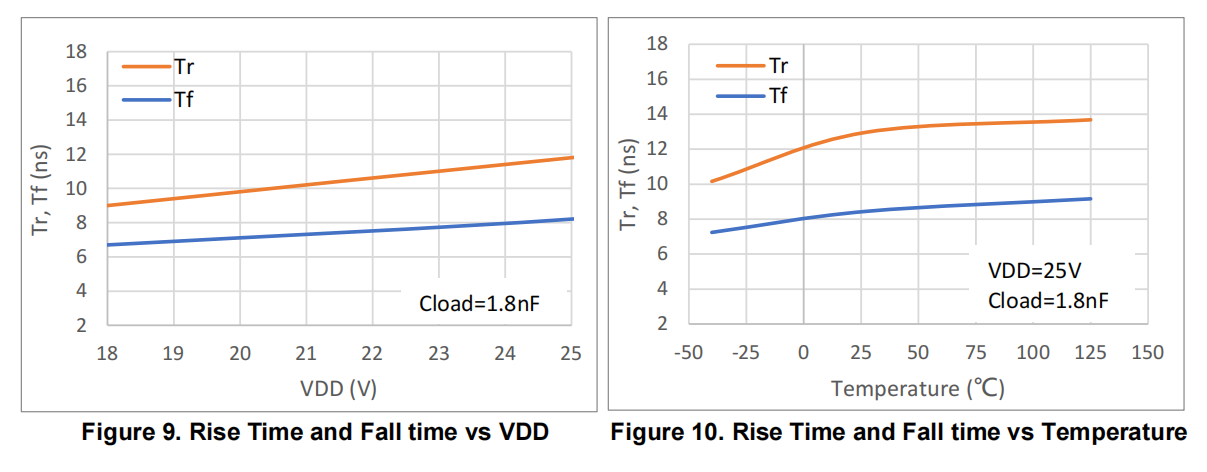

6 Tipične karakteristike

7 Detaljni opis

IVCR1402Q driver predstavlja InventChipovu najnoviju jednostruku kanalu visoke brzine low-side gate driver tehnologiju

s ugrađenom negativnom generacijom napona, zaštitom od preopterećenja/kratkog spoja,

programabilnim UVLO. Ovaj driver nudi najbolje klasične karakteristike i najkompaktniju i pouzdaniju

Upravljanje vođenjem SiC MOSFET vrata. To je prvi promisnik u industriji opremljen sva potrebna značajka za vođenje SiC MOSFET vrata

u SOIC-8 pakiranju.

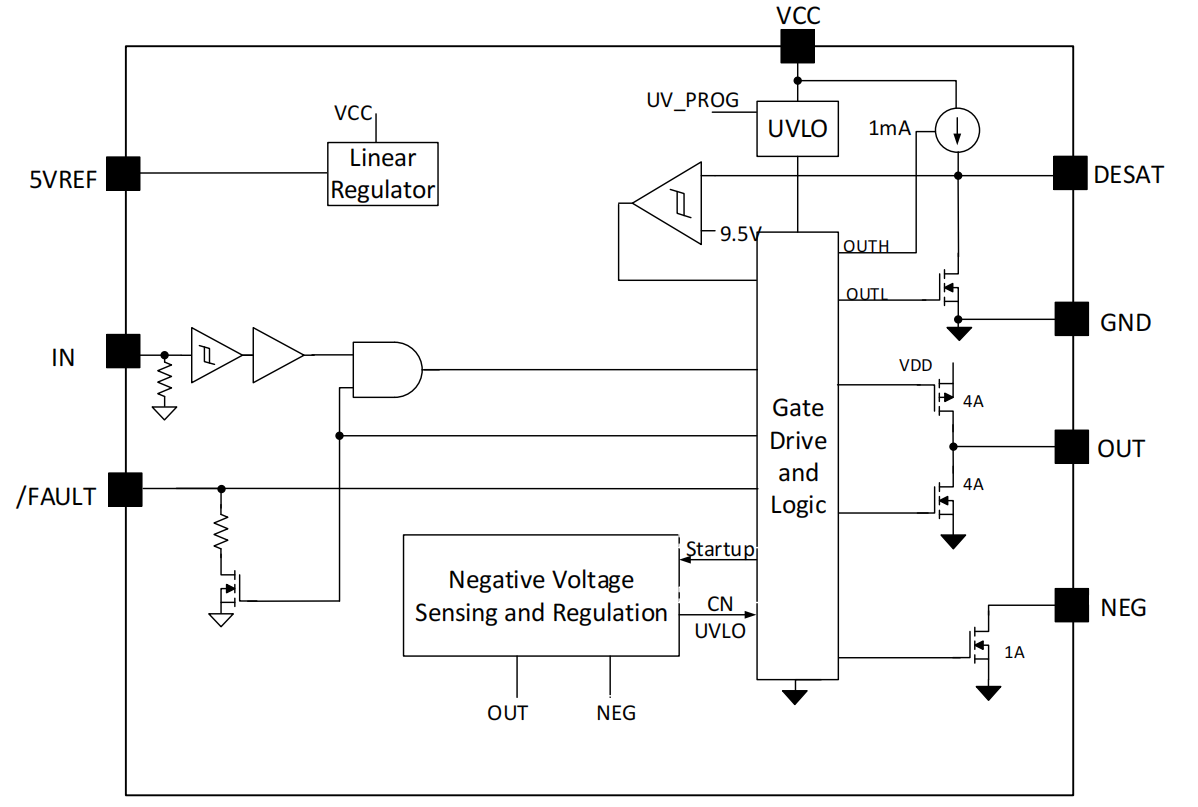

Dijagram funkcionalnog bloka

7.1 Ulaz

IN je ulaz logičkog vođenja bez inverzije. Pin ima slabi povlačni otpor. Ulaz je kompatibilan s TTL i CMOS

logičkim nivoima s maksimalnom tolerancijom ulazne napetosti od 20V.

7.2 Izlaz

IVCR1402Q ima izlaznu stanicu totem-pole od 4A. Dostavlja visoke pikovne struje izvora tamo gdje su najpotrebnije

tijekom prolaska Miller plateau područja prijelaza uključivanja moćnog prekidača. Jaka sposobnost sinkanja rezultira

vrlo nizim povlačnim impeditvom na izlazu vođenja koji poboljšava otpornost protiv parazitnih Miller efekata

učinak uključivanja, posebno gdje se koriste Si MOSFET tranzistori s nizom nabavkom na vrata ili novi širokoprugni SiC MOSFETovi

koriste.

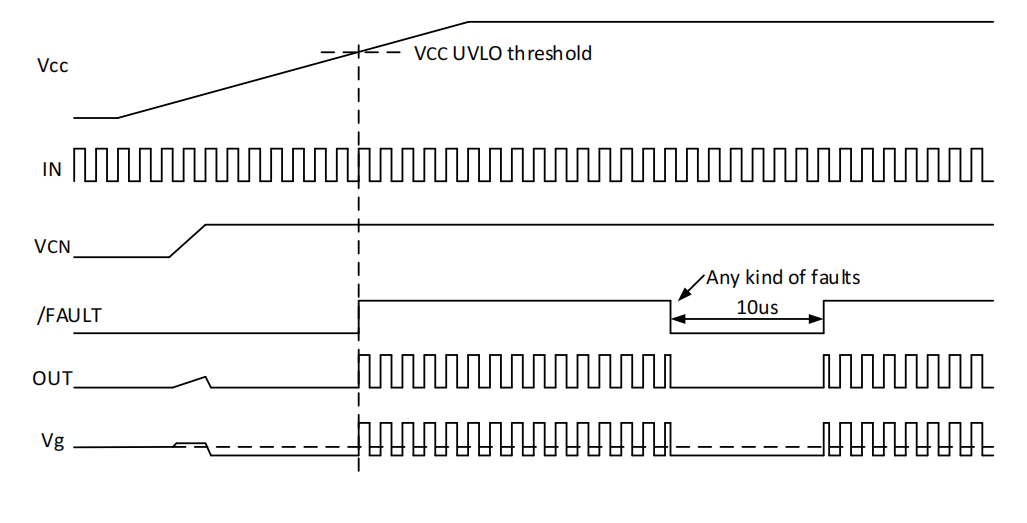

7.3 Generiranje negativnog napona

Tijekom pokretanja, izlaz NEG se povuče na GND i pruža put visokome strujnom izvoru za nabavljanje vanjskog kapacitora negativnog napona CN (tipično 1uF) preko pin-a OUT. Kapacitor može biti nabavljen na više od

2.0V u manje od 10us. Prije nego što se kapacitorski napon, VCN, nabije, \/FAULT ostaje nizak/aktiviran, ne obazirujući se na logički nivo IN-a. Nakon što je negativna polarizacija spremna, obje pine NEG i \/FAULT se otpuste i OUT počinje pratiti ulazni signal IN. Ugrađeni regulator negativnog napona regulira negativni napon na -3.5V za normalnu

radnju, neovisno o frekvenciji PWM i postotku opterećenja. Signál upravljanja vrata, NEG, zatim mijenja između

VCC-3.5V i -3.5V.

slijediti ulazni signal IN. Ugrađeni regulator negativnog napona regulira negativni napon na -3.5V za normalnu

radnju, neovisno o frekvenciji PWM i postotku opterećenja. Signál upravljanja vrata, NEG, zatim mijenja između

VCC-3.5V i -3.5V.

7.4 Zaštita od niske napone

Svi unutarnji i vanjski pomakni potencijala vozača su nadzirani kako bi se osigurala ispravna radna situacija. VCC je

nadziran od strane kola za otkrivanje niske napone. Izlaz vozača se isključuje (vuče se na nižu) ili ostaje na nižoj ako je

napona ispod postavljenog limita. Napomena: prag UVLO za VCC je 3,5V viši od gate napona.

Negativna napetost također se nadzire. Njena UVLO ima fiksni prag od 1,6V u smjeru opada. Ako dođe do poništavanja kapacitora negativne napetosti, moglo bi doći do smanjenja napetosti ispod praga. UVLO zaštita će tada vući

vrata MOSFET-a na zemlju. Kada se otkrije UVLO, \/FAULT se vuče na nižu.

MOSFET-ov vrata na masu. Vrata za FAULT se povlače na niži nivo kada se otkrije UVLO.

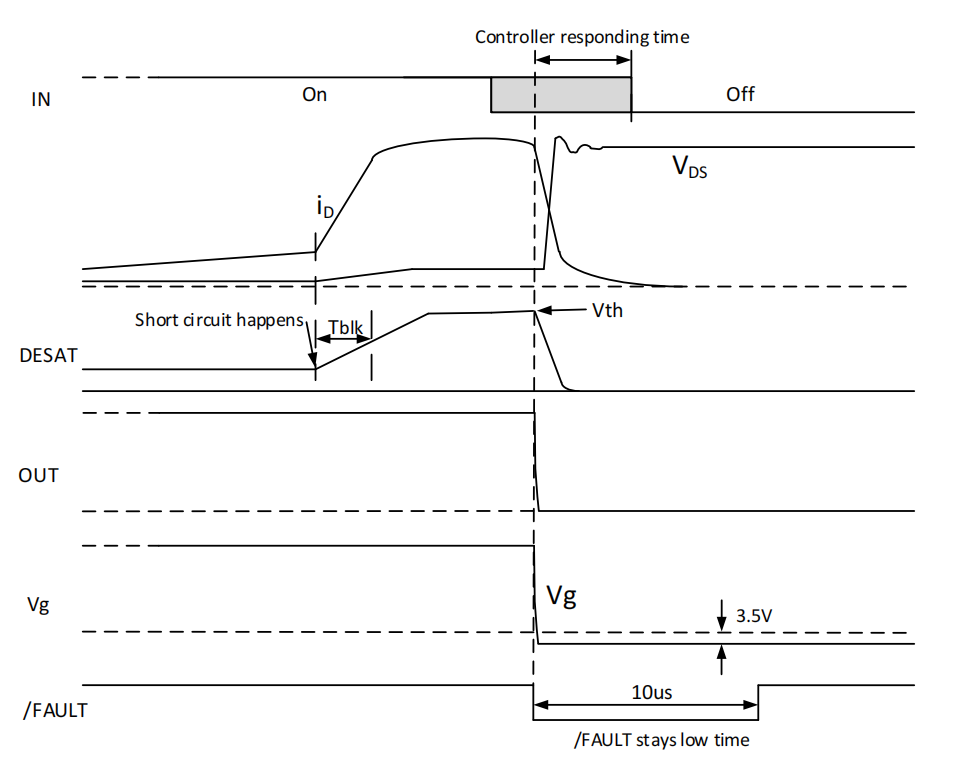

7.5 Otkrivanje desaturacije

Kada dođe do kratkog spoja ili prevelikog toka, strujanje snage uređaja (SiC MOSFET ili IGBT) može narasti do takve visoke vrijednosti da se uređaj izvodi iz stanja saturacije, a Vds\/Vce

struja može narasti do tako visoke vrijednosti da uredaji izide iz stanja satura, a Vds\/Vce od

uređaji će narasti na značajno visoku vrijednost. DESAT pin s kapacitorom za maskiranje Cblk, obično ograničen na

Id x Rds_on, sada može biti nabijen mnogo više putem unutarnjeg izvora konstantnog toka od 1mA. Kada

se napona dostigne tipična pragovna vrijednost od 9.5V, izlazi OUT i \/FAULT se oba povlače na nižu razinu. Umetnu se 200ns maskirano vrijeme

pri rastućem rubu OUT-a kako bi se spriječilo da DESAT zaštita aktivira prekasno zbog otpuštanja Coss kapaciteta.

Da bi se minimizirao gubitak unutarnjeg izvora konstantnog toka, izvor toka isključuje se kada je glavni prekidač

u isključenoj poziciji. Odabirom drugačije kapacitete, vremenski kašnjenje isključivanja (vanjsko maskirano vrijeme) može se

programirati. Maskirano vrijeme može se izračunati pomoću formule,

Teblk = Cblk ∙Vth\/ IDESAT

Na primjer, ako je Cblk 47pF, Teblk = 47pF ∙9.5V\/ 1mA = 446ns.

Napomena: Teblk već uključuje unutarnje Tblk maskirano vrijeme od 200ns.

Za postavljanje trenutne granice, može se koristiti sljedeća jednadžba,

Ilimit = (Vth – R1* IDESAT – VF_D1)\/ Rds_on

gdje je R1 programski otpor, VF_D1 je naprezna napetost visokonapornog dioda, Rds_on je upaljeno otpor SiC MOSFET-a na procijenutoj spojnoj temperaturi, kao što je 175C.

Različiti energetski sustav obično zahtjeva različito vrijeme isključivanja. Optimalno vrijeme isključivanja može maksimizirati

kratkotrajnu sposobnost sustava dok ograničuje Vds i titranje bus napetosti.

7.6 Pogreška

\/FAULT je izlaz s otvorenim kolektorom bez unutarnjeg otpornog otpora. Kada se otkrije nepuni nasitaž i podnapetost,

pinovi \/FAULT i OUT su istodobno povučeni na nižu razineu. Signal \/FAULT će ostati na nizi razine 10us nakon

uklonjene pogreške. \/FAULT je signal automatskog oporavka. Sustavni kontroler mora odlučiti kako

će reagirati.

odgovoriti na /FAULT signal. Sljedeći dijagram prikazuje niz signala.

7.7 NEG

Vanjski kapacitor negativnog pomaka brzo se napuni kada NEG opadne. To se događa tijekom uključivanja

i razdoblja ponovnog pokretanja odmah prije isteka 10µs /FAULT niske faze nakon što je otkriven bilo koji problem. Tijekom uključivanja

i razdoblja ponovnog pokretanja, mjeren je napona kapacitora negativnog pomaka VCN. Kada se napona poveća iznad VN

praga UVLO, NEG postaje visoke impendanse i OUT preuzima kontrolu nad vratom.

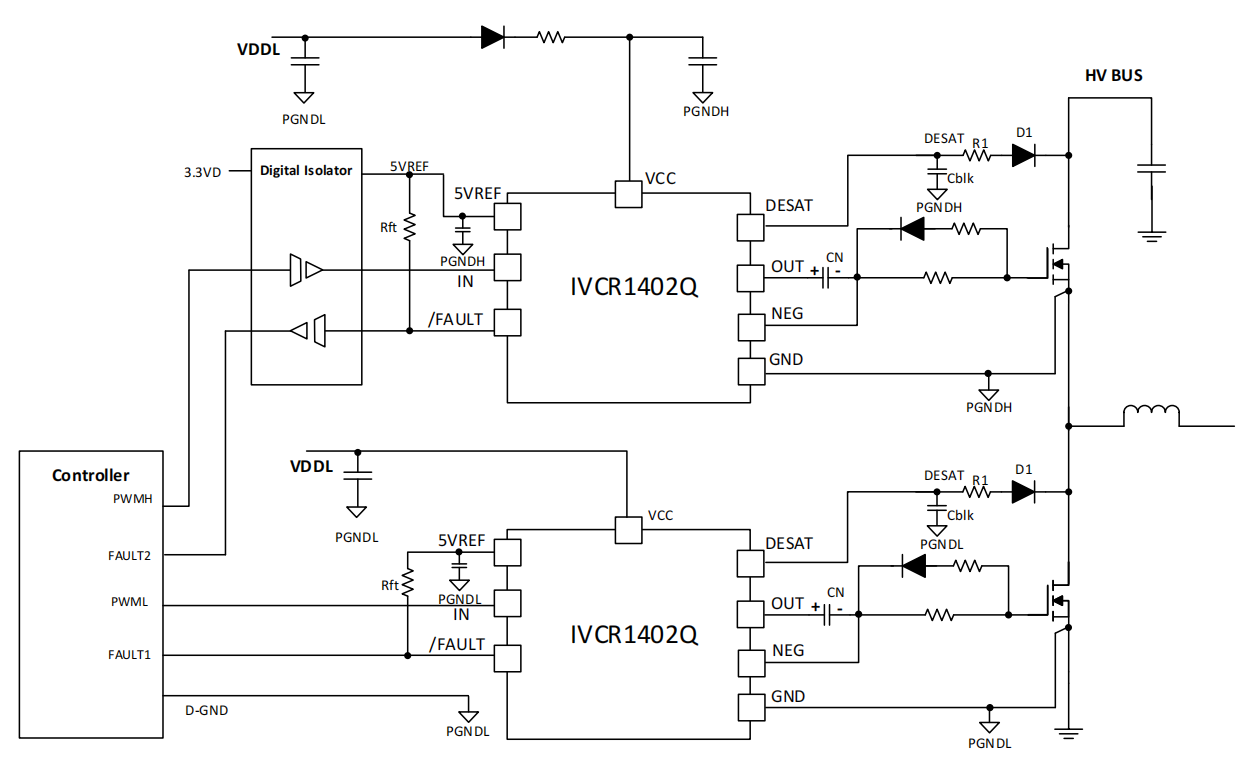

8 Primjene i implementacija

IVCR1402Q je idealni vođenik za kompaktni dizajn. To je vođenik s niskim stranom. Međutim, uz ugrađeni

generator negativnog napona, vođenik se može koristiti kao vođenik s visokom stranom bez korištenja izoliranog pomaka.

Umjesto toga može se koristiti jeftiniji bootstrap. Sljedeći shema prikazuje tipičan pol-bridge

aplikacija vozača.

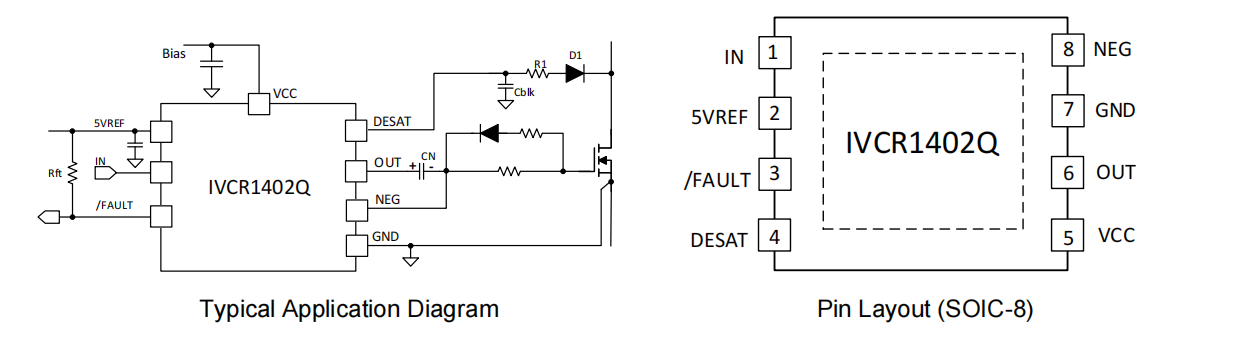

9 raspored

Dobar raspored je ključni korak za postizanje željenog performansi kruga. Cvrst tlačiški sloj je prvi korak.

Preporuča se da se otvorena pločica spoji s tlačiškom vozača. Opća pravila su da kondenzatori imaju

veći prioritet od otpornika pri raspoređivanju. 1uF i 0.1uF dekuplirajući kondenzatori

trebaju biti blizu VCC pin-a i spojeni na tlačišku ravninu vozača. Kondenzator negativnog napona treba

biti smješten blizu OUT i NEG pin-ova. Kondenzator za maskiranje treba također biti blizu vozača. Mali filter

(s konstantom vremena od 10ns) može biti potreban na ulazu IN ako se trake ulaznog signala moraju proći

kroz neke bučne područje. Sljedeći je preporučeni raspored.

10 informacije o ambalaži

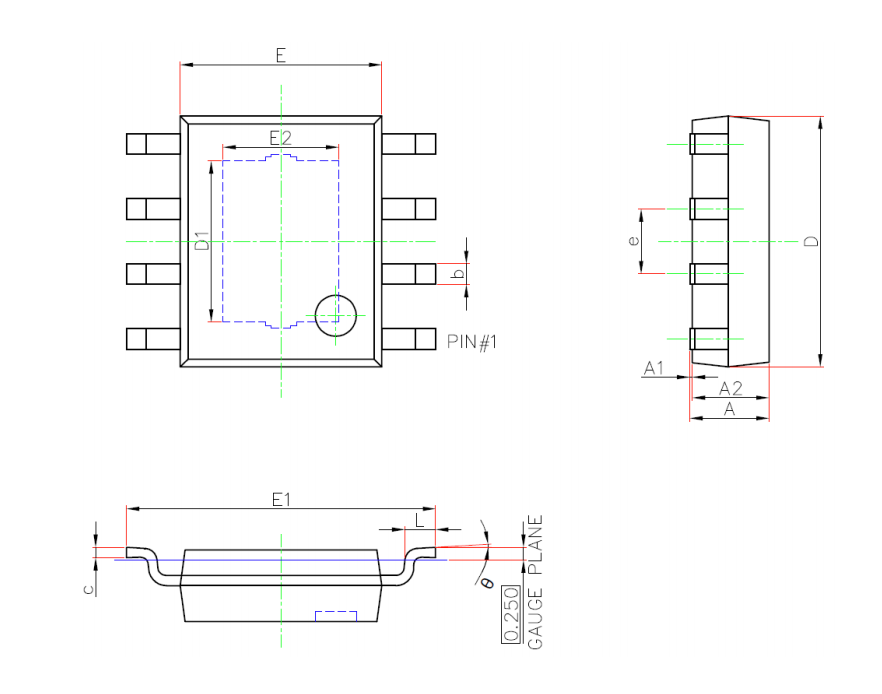

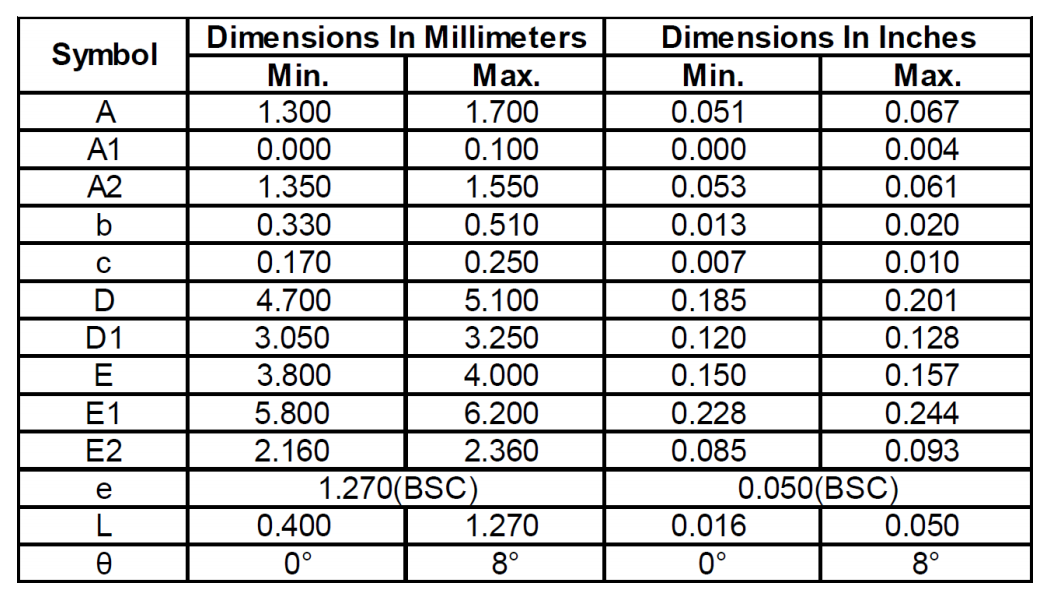

Dimenzije pakiranja SOIC-8 (EP)