| Oprindelsessted: | Zhejiang |

| Mærkenavn: | Inventchip Technology |

| Modelnummer: | IVCR1402DPQR |

| Certificering: | AEC-Q100 godkendt |

1. Egenskaber

• Drivere strømkapacitet: 4A sink og kilde top drive strøm

• Bred VCC område op til 35V

• Integreret 3.5V negativ bias

• Designet til lav side og egnet til bootstrap høj-side strøm

• UVLO for positiv og negativ spændingsdriftsspænding

• Desaturation detektion for kortslutsbeskyttelse med intern blankningstid

• Fejloutput når UVLO eller DESAT detekteres

• 5V 10mA reference for ekstern kreds, f.eks. digital isolator

• TTL- og CMOS-kompatibel indgang

• SOIC-8 med eksponeret pad til højfrekvens- og strømapplikationer

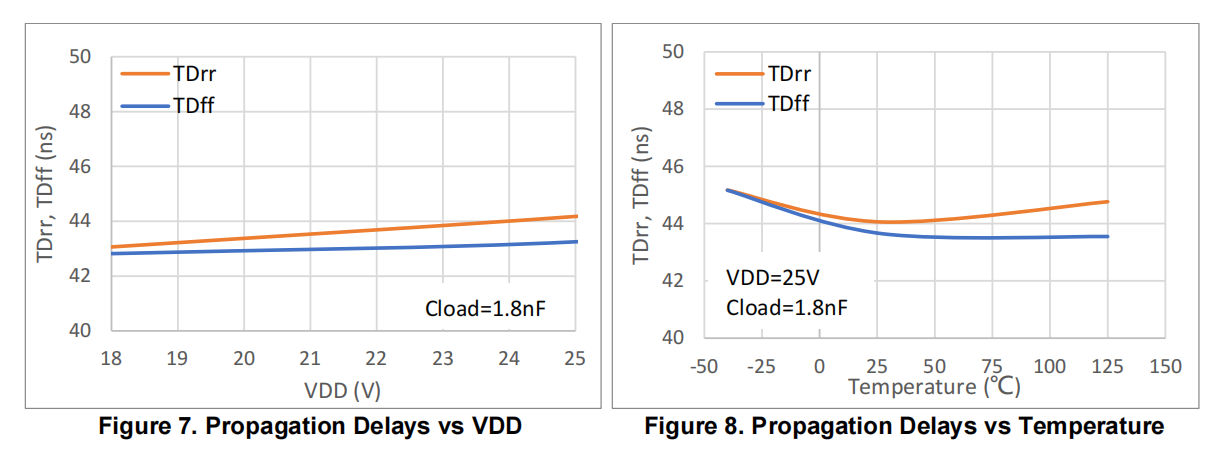

• Lav forplantningsforsinkelse 45ns typisk med indbygget de-glitch filter

• AEC-Q100 godkendt

2. Anvendelser

• EV Ombordsladere

• EV/HEV invertere og ladeanlæg

• AC/DC og DC/DC konvertere

• Motorstyring

3. Beskrivelse

IVCR1402Q er en AEC-Q100-kvalificeret, 4A enkeltkanal, højhastigheds smart driver, der effektivt og sikkert kan drevet SiC MOSFET'er og IGBT'er. Stark drivning med negativ forskydning forbedrer støjimmunitet mod Miller-effekten ved høj dv/dt drift. Udsættelseendetektering giver robust kortslutsbeskyttelse og reducerer risikoen for skader på strømforsyninger og systemkomponenter. En fast 200ns blankeringstid indføres for at forhindre, at overstrømsbeskyttelsen bliver udløst for tidligt af spids i strømmen og støj under skifting. Fast positiv gate-drejningsforings UVLO og fast negativ bias UVLO-beskyttelse sikrer sund gate operationsvoltage. Et aktivt lavt fejl-signal advarer systemet, når UVLO eller overstrøm opstår. Lav udskillelsesforsinkelse og -ulighed med en eksponeret termisk plade gør det muligt for SiC MOSFET'er at skifte på hundredevis af kHz. Integret negativ spændingsgenerering og 5V referenceudgang minimerer antallet af eksterne komponenter. Det er den første industrielle SiC MOSFET- og IGBT-driver, der inkluderer negativ spændingsgenerering, udsættelse og UVLO i en 8-pin pakke. Det er en ideal driver til en kompakt design.

Enhedsinformation

| PARTNUMBER | Pakke | Pakning | ||||||||||||||||||

| IVCR1402DPQR | SOIC-8 (EP) | Bånd og rulle | ||||||||||||||||||

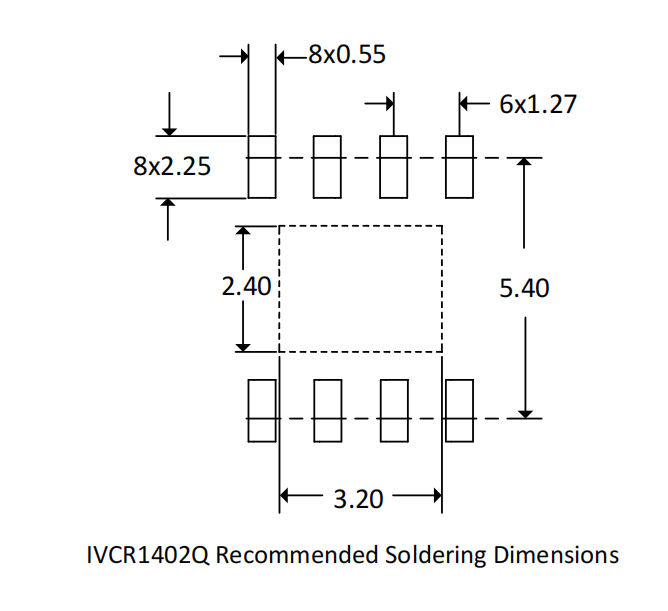

4. Pin-konfiguration og funktioner

| pin | Navn | I/O | Beskrivelse | |||||||||||||||||||||||||||||||||||||||||

| 1 | i | Jeg | Logikindgang | |||||||||||||||||||||||||||||||||||||||||

| 2 | 5VREF | O | 5V/10mA output til ekstern kreds | |||||||||||||||||||||||||||||||||||||||||

| 3 | /FAULT | O | Åben kollektor fejloutput, trækkes ned når overstrøm eller UVLO registreres. | |||||||||||||||||||||||||||||||||||||||||

| 4 | DESAT | Jeg | Udsattningsdetektionsindgang | |||||||||||||||||||||||||||||||||||||||||

| 5 | VCC | p | Positiv spændingsforsyning | |||||||||||||||||||||||||||||||||||||||||

| 6 | ud | O | Gatespændingsudgang | |||||||||||||||||||||||||||||||||||||||||

| 7 | GND | G | Drivertilslutning til jord | |||||||||||||||||||||||||||||||||||||||||

| 8 | NEG | O | Negativ spændingsudgang | |||||||||||||||||||||||||||||||||||||||||

| Eksponeret patte | Bundens eksponerede patte er ofte forbundet til GND i layout. | |||||||||||||||||||||||||||||||||||||||||||

5. Specificeringer

5.1 Absolutte maksimale værdier

Over fri-luft temperaturområde (med mindre andet er angivet) (1)

| min max | enhed | ||||||||||||||||||||||||||||||||||||||||||

| VCC Total forsyningsspænding (reference til GND) | -0.3 35 | V | |||||||||||||||||||||||||||||||||||||||||

| VOUT Gate driver output spænding | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| IOUTH Gate driver output kildestrøm (ved maks pulsbredde 10us og 0.2% cyklusforhold) | 6.6 | A. | |||||||||||||||||||||||||||||||||||||||||

| IOUTL Gate driver output modtagelsesstrøm (ved maks pulsbredde 10us og 0.2% cyklusforhold) | 6.6 | A. | |||||||||||||||||||||||||||||||||||||||||

| VIN IN signal spænding | -5.0 20 | V | |||||||||||||||||||||||||||||||||||||||||

| I5VREF 5VREF output strøm | 25 | - Hvad? | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Spænding ved DESAT | -0.3 VCC+0.3 | V | |||||||||||||||||||||||||||||||||||||||||

| VNEG Spænding på NEG-pin | OUT-5,0 VCC+0,3 | V | |||||||||||||||||||||||||||||||||||||||||

| TJ Forbindelsestemperatur | -40 150 | °C | |||||||||||||||||||||||||||||||||||||||||

| TSTG Lagringstemperatur | -65 150 | °C | |||||||||||||||||||||||||||||||||||||||||

(1) Drift uden for de angivne absolutte maksimale værdier kan forårsage permanent skade på enheden.

Eksponering for absolutte maksimale vilkår i længere tid kan påvirke enhedens pålidelighed.

5,2 ESD-vurdering

| værdi | enhed | |||||||||||||||||||||||||||||||||||||||||||

| V(ESD) Elektrostatiske afslag | Model af menneskelig krop (HBM), i overensstemmelse med AEC Q100-002 | +/-2000 | V | |||||||||||||||||||||||||||||||||||||||||

| Model af opladet enhed (CDM), i overensstemmelse med AEC Q100-011 | +/-500 | |||||||||||||||||||||||||||||||||||||||||||

5.3 Anbefalede driftsforhold

| min | max | enhed | ||||||||||||||||||||||||||||||||||||||||||

| VCC Total forsyningsspænding (reference til GND) | 15 | 25 | V | |||||||||||||||||||||||||||||||||||||||||

| VIN Gate input spænding | 0 | 15 | V | |||||||||||||||||||||||||||||||||||||||||

| VDESAT Spænding ved DESAT | 0 | VCC | V | |||||||||||||||||||||||||||||||||||||||||

| TAMB Miljøtemperatur | -40 | 125 | °C | |||||||||||||||||||||||||||||||||||||||||

5.4 Termisk information

| IVCR1402DPQR | enhed | ||||||||||||||||||||||||||||||||||||||||||

| RθJA Forbindelse til miljøet | 39 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJB Kobling fra junction til PCB | 11 | °C/W | |||||||||||||||||||||||||||||||||||||||||

| RθJP Kobling fra junction til eksponeret pad | 5.1 | °C/W | |||||||||||||||||||||||||||||||||||||||||

5.5 Elektriske specifikationer

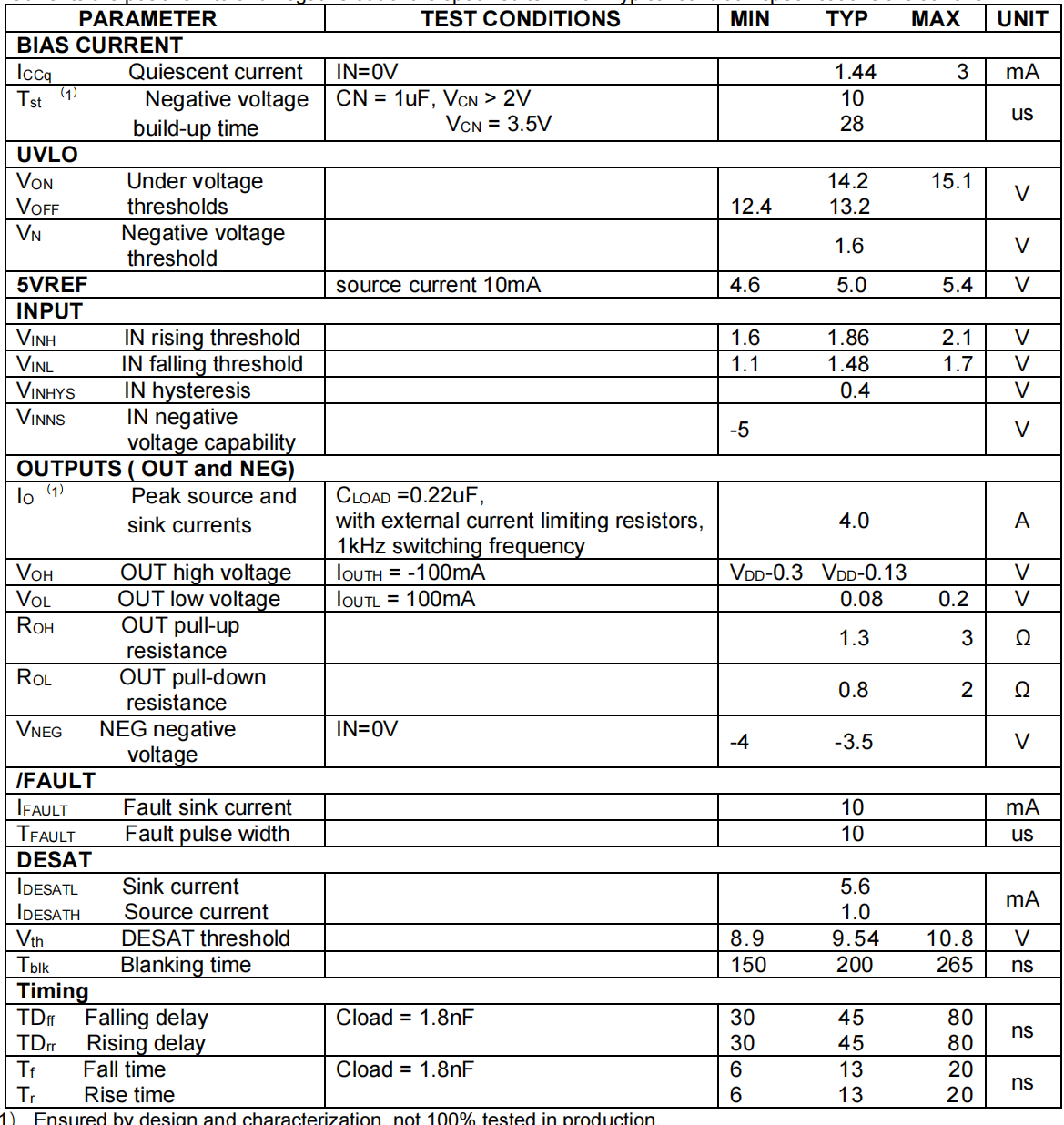

Med mindre andet er angivet, VCC = 25 V, TA = –40°C til 125°C, 1-μF bypass kapacitet fra VCC til GND, f = 100 kHz.

Strømme er positive ind i og negative ud af den angivne terminal. Typiske betingelsespecifikationer er på 25°C.

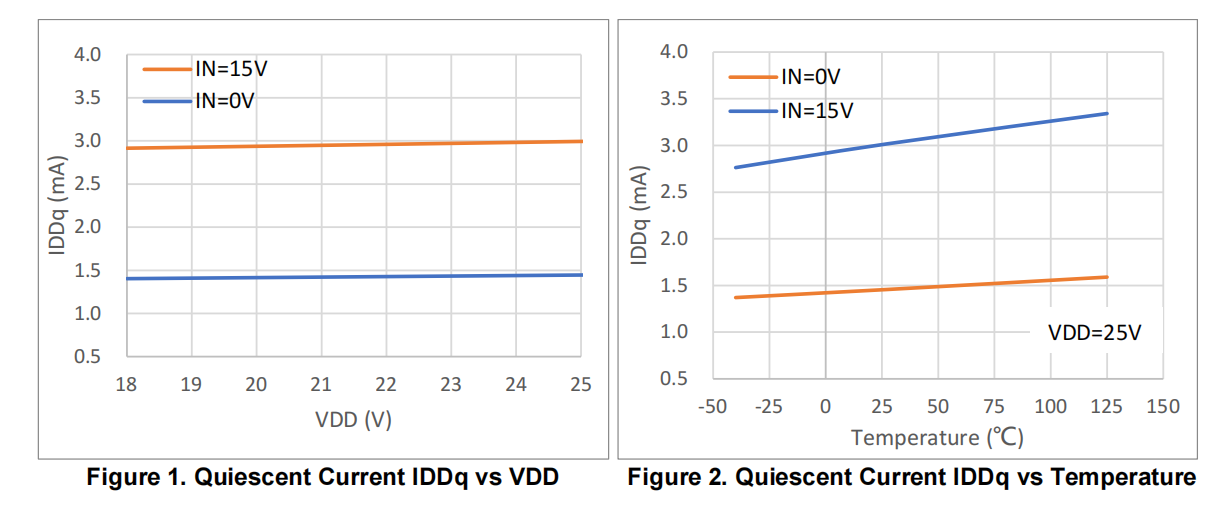

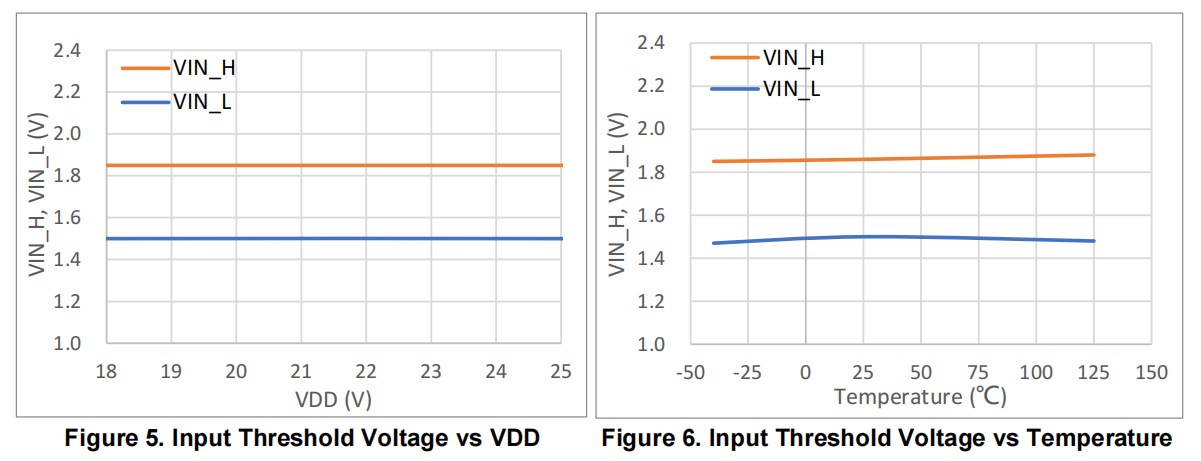

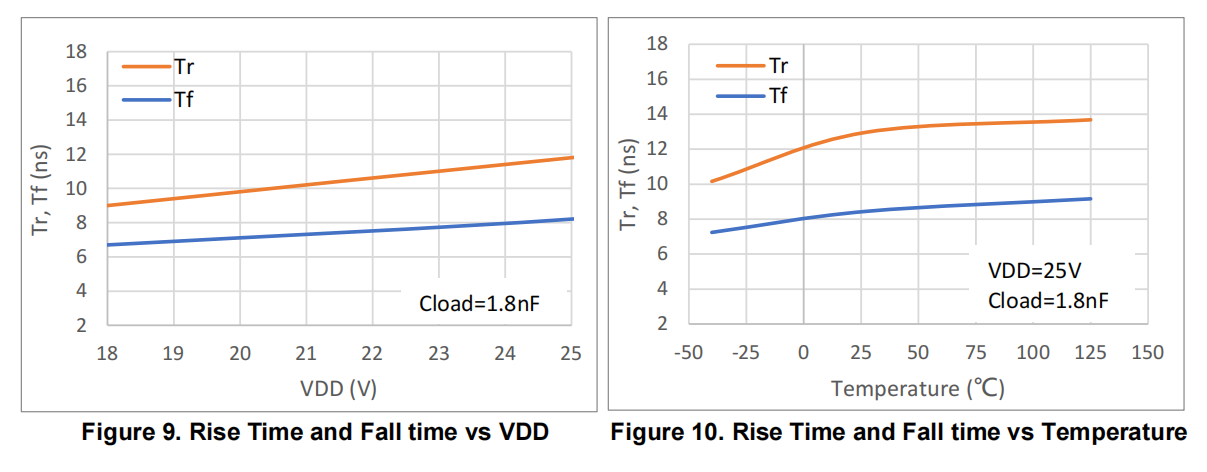

6 Typiske karakteristika

7 Detaljerede beskrivelse

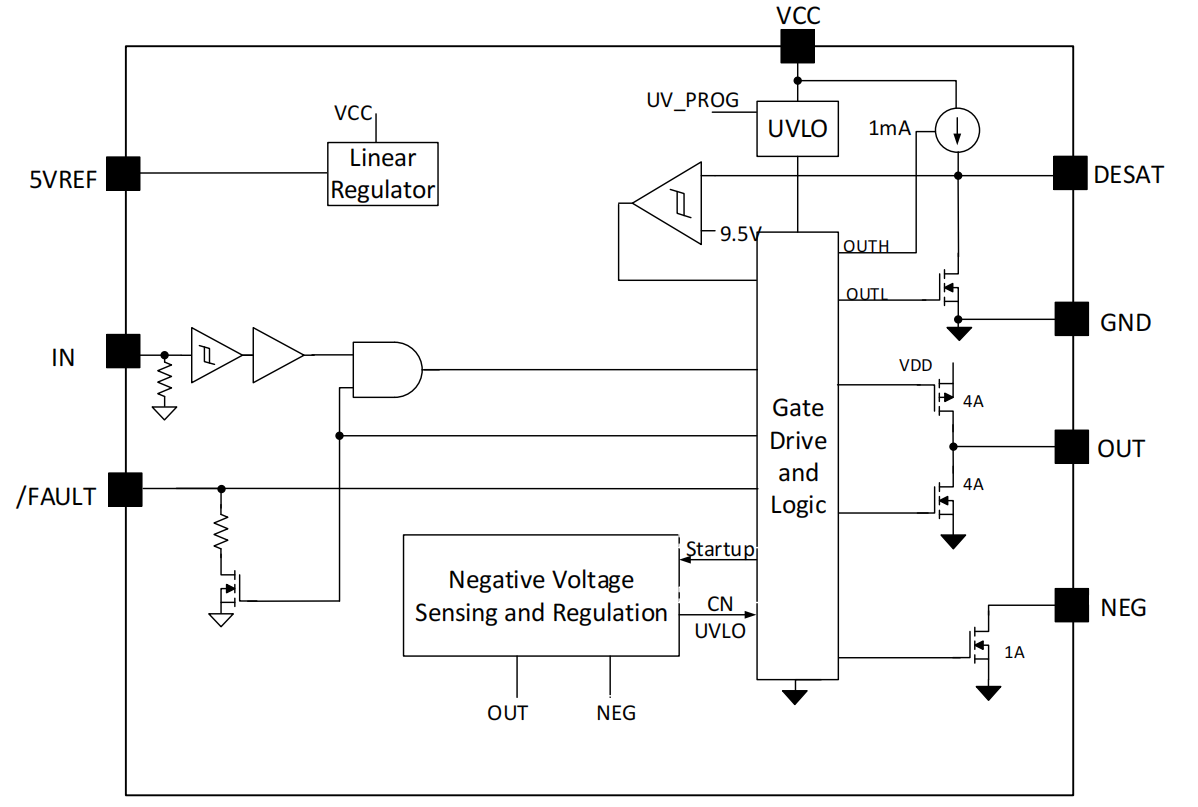

IVCR1402Q driver repræsenterer InventChips fremmede enkeltkanals lavside højhastigheds gate driver

teknologiudvikling. Den har indbygget negativ spændingsgenerering, desaturations/skyde-cirkuits beskyttelse,

programmerbar UVLO. Denne driver tilbyder topklasse karakteristika og den mest kompakte og pålidelige

SiC MOSFET gate drevskontrol. Det er den første industriedriver, der er udstyret med alle nødvendige SiC MOSFET gate

drevsfeatures i en SOIC-8 pakke.

Funktionsblokdiagram

7.1 Input

IN er en logisk, ikke-inverterende gate-driver input. Pin'en har en svag pulldown. Inputtet er et TTL og CMOS

kompatibelt logikniveau med maksimal 20V inputtolerance.

7.2 Output

IVCR1402Q har en 4A totem-pole output stage. Den leverer høj top-kildestrøm, når det er mest

nødvendigt under Miller plateau området af power-switchens tænd-overgang. Stærk sink evne resulterer i

en meget lav pull-down impedans i driverens output stage, hvilket forbedrer immunforsvaret mod parasitære Miller

tændnings-effekt, især hvor lav gate-gebyr Si MOSFET'er eller de nye brede bandgap SiC MOSFET'er er

brugt.

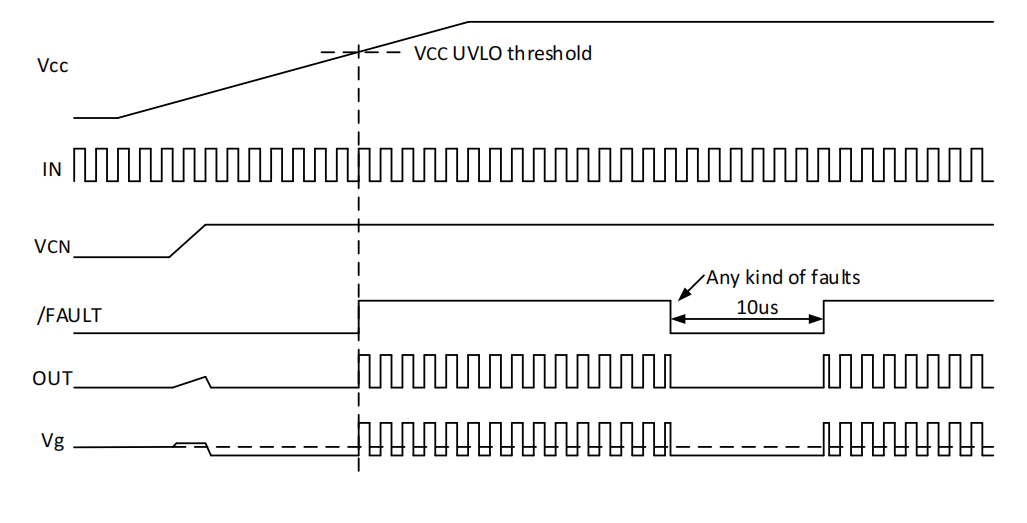

7.3 Generering af Negativ Spænding

Ved opstart trækkes NEG-output til GND og giver en høj strømsti for en strømkilde til at oplade den

eksterne negative-spændings-kondensator CN (1uF typisk) gennem OUT-pin. Kondensatoren kan oplades til over

2.0V på mindre end 10us. Før kondensator-spændingen, VCN, er blevet opladt, forbliver \/FAULT lavt/aktivt, uanset

IN's logiske niveau. Når den negative spænding er klar, frigives både NEG-pin og \/FAULT-pin og OUT begynder at

følge input-signalet IN. En indbygget negativ spændingsregulator regulerer den negative spænding til -3.5V for normal

drift, uanset PWM-hyppighed og -dutycykel. Gate-drivningsignalet, NEG, skifter derefter mellem

VCC-3.5V og -3.5V.

7.4 Under-SpændingsBeskyttelse

Alle interne og eksterne forskydninger i drivere bliver overvåget for at sikre en sund driftsforhold. VCC er

overvåget af en under-speningsdetektorcirkuit. Drevets output slukkes (trækkes lav) eller forbliver lav, hvis

spændingen er under den indstillede grænse. Bemærk at VCC UVLO-grænse er 3,5V højere end gategespeninger.

Den negative spænding overvåges også. Dens UVLO har en fast 1,6V negativ gående grænse. En fejl i kapaciteten

for den negative spænding kan føre til, at kapacitets-spændingen falder under grænsen. UVLO-sikringen vil

derefter trække MOSFET’s gate ned til jorden. \/FAULT trækkes lav, når UVLO opdages.

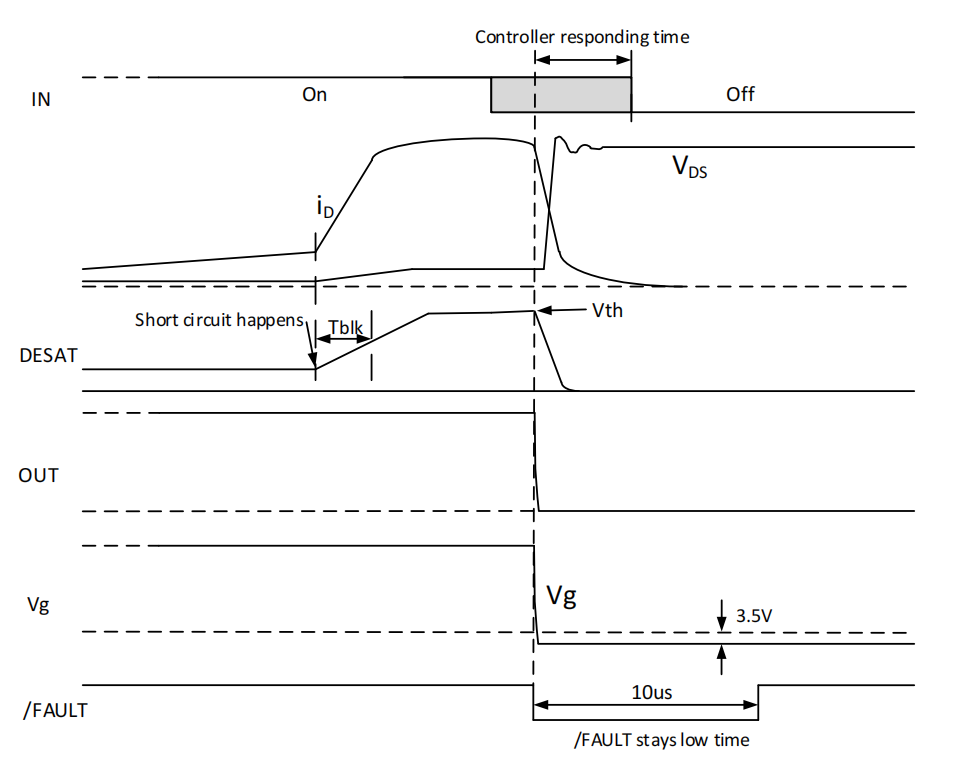

7,5 Udsatningsdetektion

Når der opstår kortslutning eller overstrøm, kan strømmen i det magtesystem (SiC MOSFET eller IGBT) stige

så meget, at enhederne kommer ud af satureret tilstand, og Vds\/Vce for enhederne vil stige markant. DESAT-pin

med en blankingskapacitor Cblk, normalt clamped til

Id x Rds_on kan nu oplade meget højere ved hjælp af en intern 1mA konstant strømkilde. Når spændingen

når typisk 9,5V terskel, drages både OUT og /FAULT lav. En 200ns blank tidsperiode indsættes

ved stigende flanke på OUT for at forhindre, at DESAT beskyttelseskredsen bliver udløst for tidligt på grund af Coss afladning.

For at minimere tabet af den interne konstant strømkilde, slukkes strømkilden, når hovedskruen

er i slukket tilstand. Ved valg af en anden kapacitet kan slukkets forsinkelsestid (ekstern blankingstid) programmieres.

Blankingstiden kan beregnes med

Teblk = Cblk ∙Vth / IDESAT

For eksempel, hvis Cblk er 47pF, Teblk = 47pF ∙9,5V / 1mA = 446ns.

Bemærk, at Teblk allerede indeholder den interne Tblk 200ns blankingstid.

For indstilling af strømegrænsen kan følgende ligning bruges,

Ilimit = (Vth – R1* IDESAT – VF_D1)\/ Rds_on

hvor R1 er en programmeringsresistor, VF_D1 er højspændingsdiode fremadsspanning, Rds_on er SiC MOSFET slukketilstand

modstandsvideregang ved estimeret forbindelses temperatur, såsom 175C.

Et andet strømsystem kræver normalt en anden slukketid. En optimeret slukketid kan maksimere

systemets kortsluts kapacitet, samtidig med at der begrænses Vds og bus spændingsringing.

7.6 Fejl

\/FAULT er en åben kollektor output uden intern trækop modstand. Når desaturation og lavspændinger

bliver registreret, slås både \/FAULT pin og OUT ned. \/FAULT signal vil forblive lav i 10us efter

fejlen er fjernet. \/FAULT er et automatisk genopretningssignal. Systemkontrolleren skal afgøre hvordan

man reagerer på \/FAULT signal. Følgende diagram viser signalsekvensen.

7.7 NEG

Den eksterne negative spændingskondensator oplades hurtigt, når NEG går lav. Det sker under opstart

og genstart periode lige før 10us /FAULT lav periode udløber efter at en fejl er opdaget. Under opstart

og genstart periode måles den negative spændingskondensator spænding VCN. Så snart spændingen overstiger VN

UVLO terskel, bliver NEG høj-impedans og OUT overtager dørstyring.

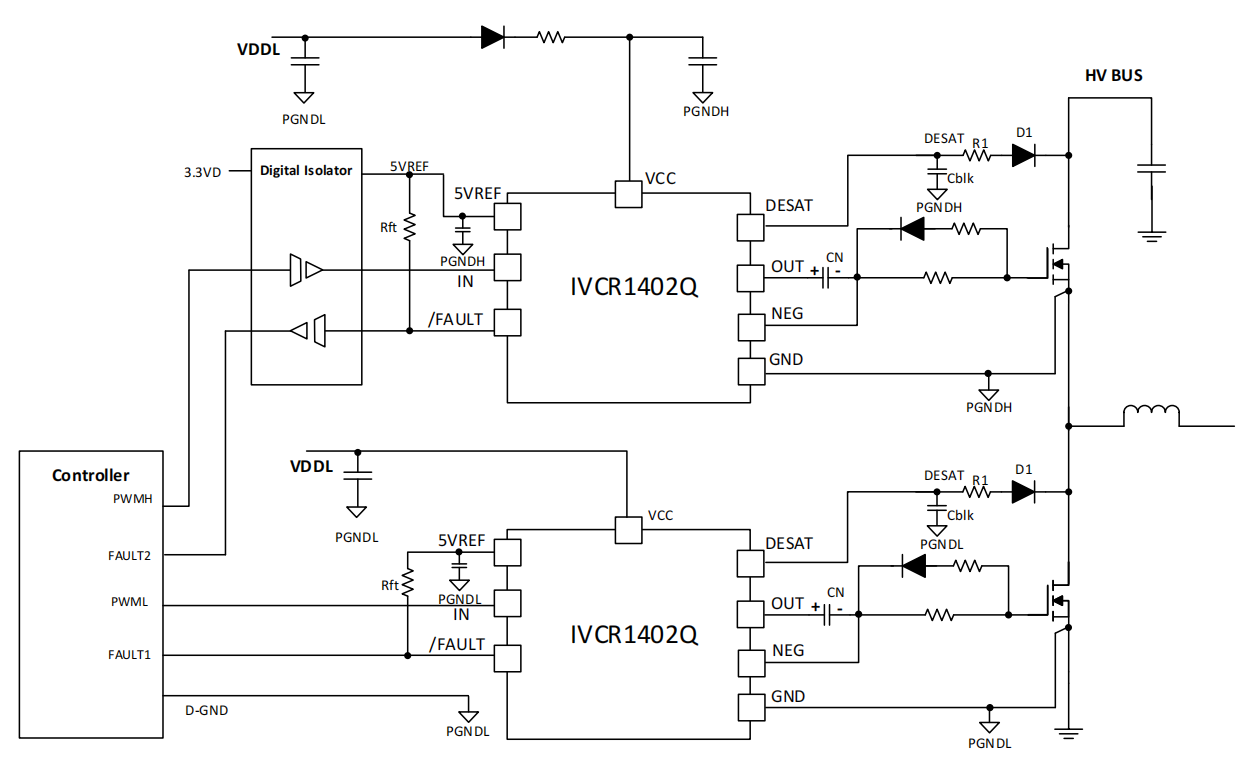

8 Anvendelser og implementering

IVCR1402Q er en ideel driver for en kompakt design. Det er en low-side driver. Med en indbygget

negativ spændingsgenerator kan drivere bruges som en high-side driver uden at bruge en isoleret bias.

En billig bootstrap kan så bruges i stedet. Følgende circuitskema viser en typisk halvbridge

driver applikation.

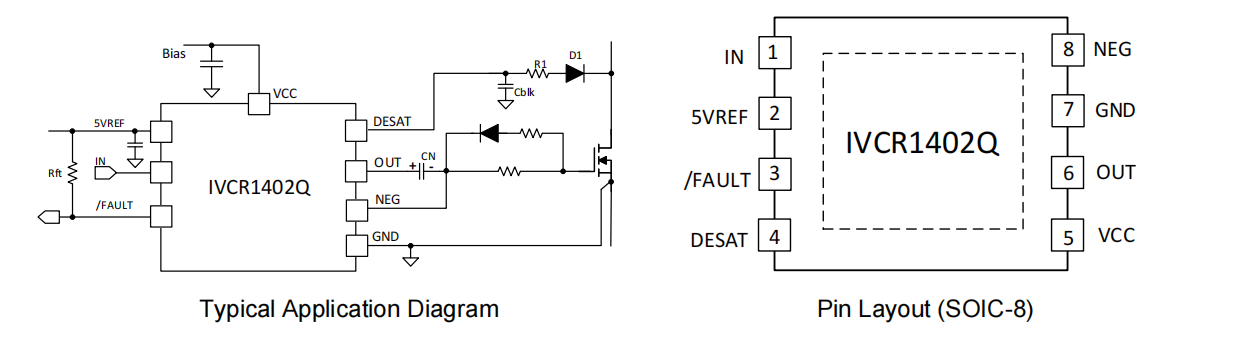

9 Layout

Et godt layout er et nøglets skridt for at opnå den ønskede cirkuitydelse. Fast jord er det første at starte med.

Det anbefales at forbinde det eksponerede pad til driverejorden. Det er en almindelig regel, at kondensatorer har

en højere prioritet end motstande ved placering. En 1uF og en 0.1uF decoupling-kondensator

skal være tæt på VCC-pin og jordes til driverejorden. Negativ spændingskondensator skal

placeres tæt på OUT og NEG-piner. Blankingskondensator skal også være tæt på driveren. En lille filter

(med 10ns tidskonstant) kan være nødvendig ved indgangen af IN, hvis indgangsspor må passere

gennem nogle støjede områder. Herunder er et anbefalet layout.

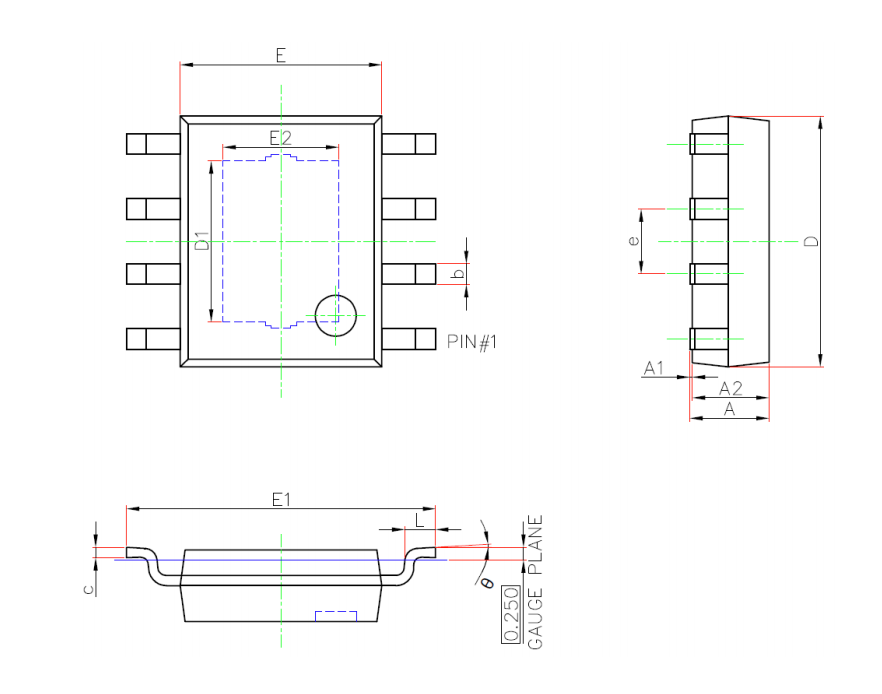

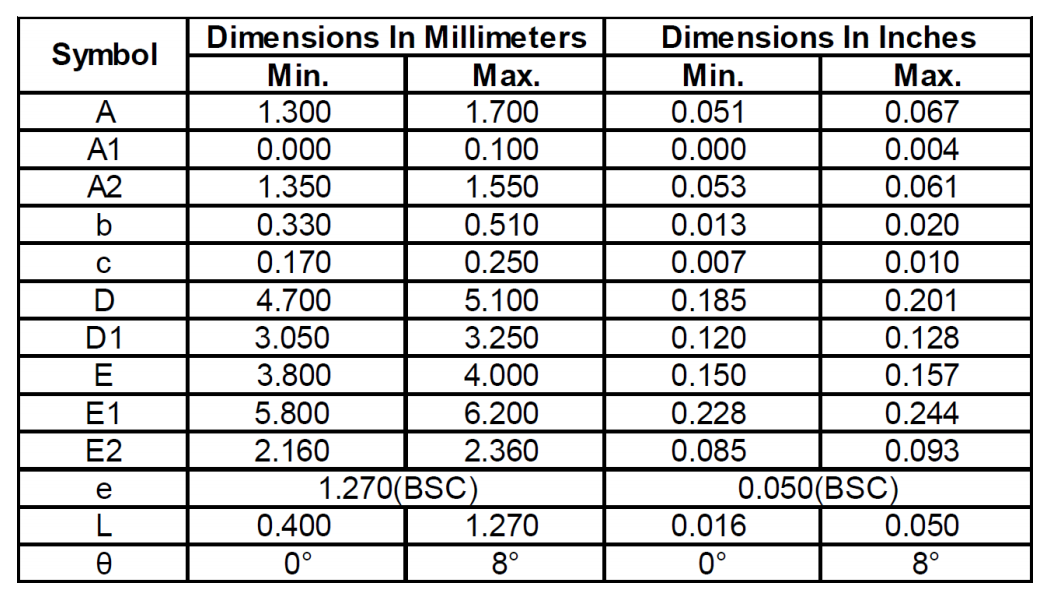

10 Pakkeinformation

SOIC-8 (EP) Pakkemål